Part Number: AM2634

Other Parts Discussed in Thread: TMS570LS1227, SYSCONFIG,

Tool/software:

Hello,

I am currently working on porting firmware from the TMS570LS1227. One of the modules requires data sharing between the firmware and the SBL, so that the UDS transaction initialized in the firmware can be completed in the bootloader. This enables the firmware update to be handled by the SBL afterward.

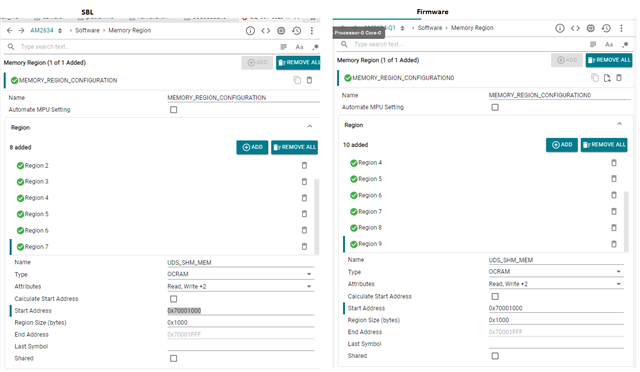

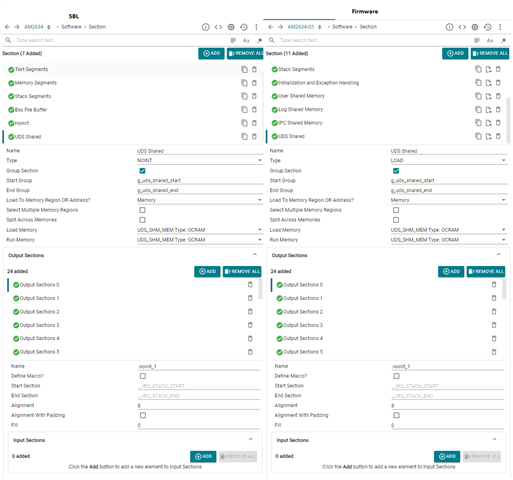

I have used SysConfig to define the UDS_SHM_MEM memory region and the UDS shared section in both the bootloader and firmware projects (see the picture below).

Initially, I implemented a watchdog reset in the firmware. However, after the reset, the RAM content is not retained, and all memory locations are initialized to 0.

After searching the forum, I came across the following post.

Instead of using the watchdog reset, I tried performing a software warm reset instead (via the function call SOC_generateSwWarmReset()). Unfortunately, this did not resolve the issue, and the memory is still initialized to 0.

From my experience with the TMS570LS1227, I recall needing to customize the assembler initialization code. However, after reviewing the AM2634 code, I do not see anything that would require modification.

What is the correct way to implement RAM sharing between the firmware and the SBL, ensuring that the RAM retains its content?

Kind regards,