Part Number: MCU-PLUS-SDK-AM263PX

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

We are using UART DMA to transmit and receive data between the TI AM263Px and a modem, based on the example code: uart_echo_dma_lld_am263px-cc_r5fss0-0_nortos_ti-arm-clang.

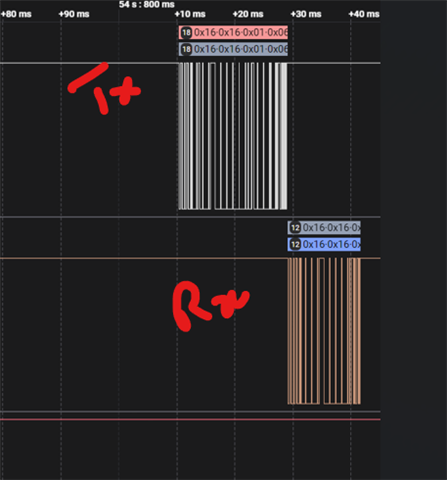

Using a logic analyzer to monitor the TX and RX pins, we observed the following behavior:

When we transmit predefined data (18 bytes) to the modem, we immediately receive a response of 12 bytes from the modem.

As per our application requirements, we need to read this 12-byte response in two stages:

- First, read 1 byte

- Then, read the remaining 11 bytes

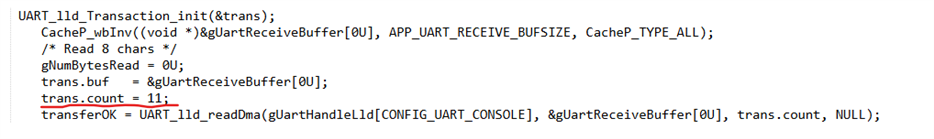

We are successfully receiving the first byte and getting a receive completion interrupt. However, during the second read attempt, we are not receiving remaining bytes as expected.