Other Parts Discussed in Thread: AM2632

Tool/software:

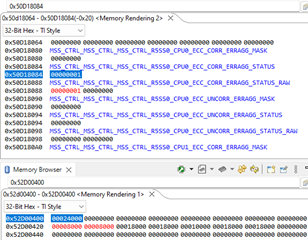

When 1 bit error is injected in ATCM R5SS0 memory and read memory to trigger ECC error. This will set following registers

MSS_CTRL

Set 50D18084h and 50D18088h for 1 bit error

Set 50D18094h and 50D18098h for 2 bit error

ESM

Set 52D00420h and 52D00424h for ECC Core 0.

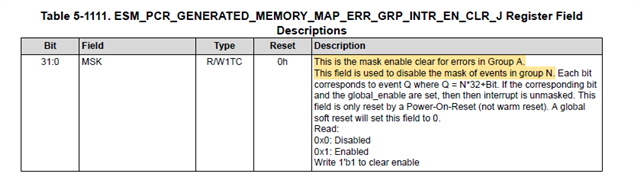

According to SDK sdl_ecc_r5_atcm0 example, to clear TCM errors, writing 1 to 0x50D18084h and 0x50D18088h for 1 bit error and writing 1 to 0x52D0042C (ESM_PCR_GENERATED_MEMORY_MAP_ERR_GRP_INTR_EN_CLR_J Register).

This will reset 0x52D00424h but 0x52D00420h is still set to 1.

How to reset the 0x52D00420h ESM_PCR_GENERATED_MEMORY_MAP_ERR_GRP_RAW_J Register to clear TCM errors?