Part Number: AM2432

Other Parts Discussed in Thread: TMDS243EVM

Tool/software:

Hello,

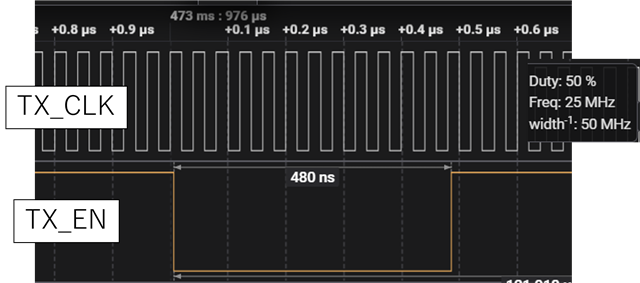

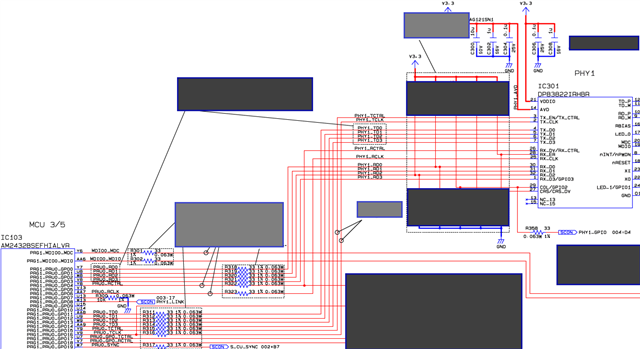

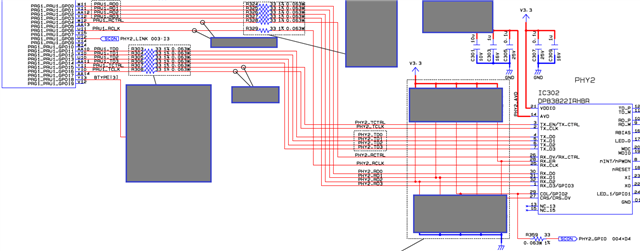

On a custom board using AM2432, I'm experiencing an issue where the 100M Ethernet IPG is set to 480ns.

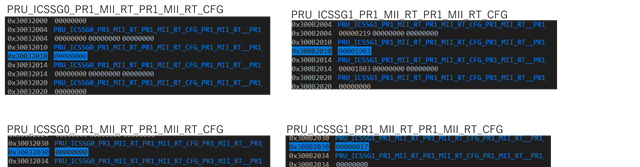

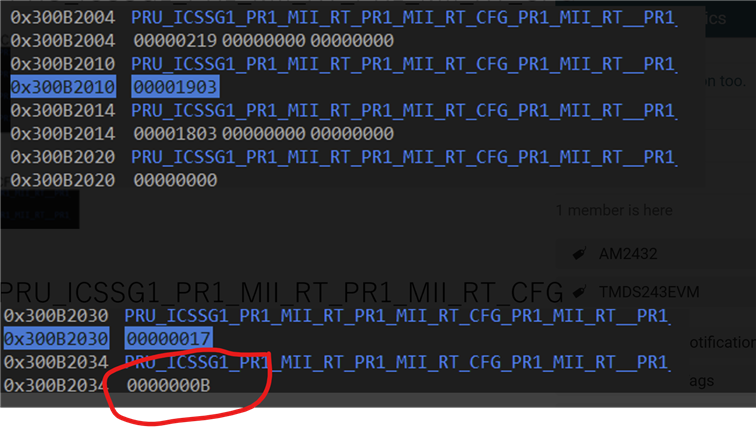

After some research, I found that IPG can be set to 960ns by changing TX_IPG1 register 0x0x30032034 from 0x0B to 0x17, instead of TX_IPG0 register 0x0x30032030.

I would like to analyze why this is happening and whether the cause lies in the firmware, SDK, or hardware,

so could you please tell me which module is using this TX_IPG register to adjust the IPG?

Regards,

Nishimori