Part Number: AM2631

Other Parts Discussed in Thread: UNIFLASH,

Tool/software:

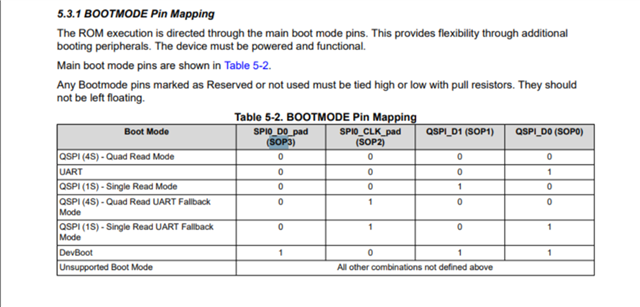

We are currently using UniFlash to flash code onto the AM2631. Typically, we set the SOP switches to enable DevBoot mode (SOP0, SOP1, SOP3 = OFF; SOP2 = ON) before flashing, and after the process is complete, we switch all SOPs to ON. This process works reliably.

However, to simplify operations, we tried flashing without changing the SOP switches — i.e., leaving the system in QSPI(4S) - Quad Read Mode. In this mode, we noticed the following behavior:

-

Flashing does work, but often fails partway through, requiring a second attempt.

-

Interestingly, with some software versions, such as B002, flashing succeeds every time (20 out of 20 attempts).

-

But with version B003, flashing fails on the first try every time, and only succeeds after retrying.

From our understanding, when the system is in QSPI(4S) mode, the QSPI RBL (ROM Bootloader) runs automatically, loading and executing the SBL from flash. During this process, internal registers or configurations may be modified, potentially interfering with the flashing process.

In contrast, DevBoot mode skips the RBL entirely, avoiding any such side effects, which makes it the most reliable option for flashing.

Therefore, we would like to confirm:

-

Is DevBoot mode always recommended when flashing with UniFlash to avoid such failures?

-

Is flashing in QSPI(4S) mode inherently unstable due to the RBL/SBL possibly altering chip state?

-

Given that the behavior differs between versions (e.g., B002 vs. B003), is the flashing failure more likely caused by:

-

The bootloader interfering due to QSPI mode?

-

Or specific changes in the software versions themselves?

-

-

Ultimately, is it mandatory to set the SOP switches to DevBoot mode every time we flash?

-

Or is flashing without changing SOP switches (i.e., in QSPI mode) considered acceptable under certain conditions?

-

We want to determine whether this issue is software-related or an inherent limitation of not setting the SOPs to DevBoot.

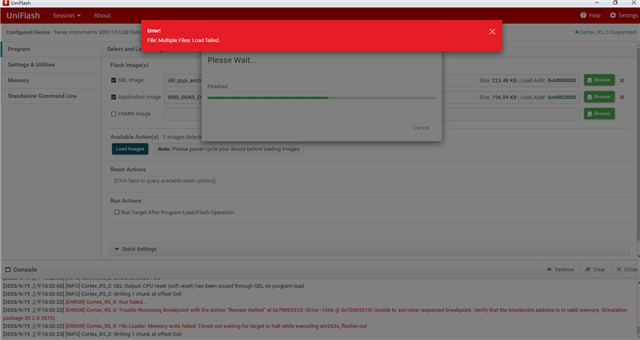

Below are the screenshots of the BootMode PIN settings we are using, as well as the log records when flashing fails.

////first flashing fail log: [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched*** [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: AM263x Initialization Scripts Launched. Please Wait... [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: AM263x_Cryst_Clock_Loss_Status() Launched [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Crystal Clock present [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: AM263x_SOP_Mode() Launched [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: SOP MODE = 0x00000000 [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: QSPI - 4S Functional boot mode [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: AM263x_Read_Device_Type() Launched [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: AM263x_Check_supported_mode() Launched [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: The Device supports Lockstep mode [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: mode = 0 [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: *** R5FSS0 Lockstep Reset *** [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: *** R5FSS1 Lockstep Reset *** [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: R5F ROM Eclipse [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: R5FSS0_0 Released [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: R5FSS0_1 Released [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: R5FSS1_0 Released [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: R5FSS1_1 Released [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: All R5F Cores Released for program load [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: L2 Mem Init Complete [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MailBox Mem Init Complete [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: *********** R5FSS0/1 Lockstep mode Configured******** [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: CORE PLL Configuration Complete [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: SYS_CLK DIVBY2 [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: CLK Programmed R5F=400MHz and SYS_CLK=200MHz [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: *** Enabling Peripheral Clocks *** [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: RTI0 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: RTI1 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: RTI2 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: RTI3 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: WDT0 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: WDT1 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: WDT2 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: WDT3 Clock Enabled (200MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: LIN0_UART0 Clock Enabled (160MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: LIN1_UART1 Clock Enabled (160MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: LIN2_UART2 Clock Enabled (160MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: LIN3_UART3 Clock Enabled (160MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: LIN4_UART4 Clock Enabled (160MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: LIN5_UART5 Clock Enabled (160MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling QSPI Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: QSPI0 Clock Enabled (80MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling I2C Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: I2C Clock Enabled (48MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling TRACE Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Trace Clock Enabled (250MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCAN0 Clock Enabled (80MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCAN1 Clock Enabled (80MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCAN2 Clock Enabled (80MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCAN3 Clock Enabled (80MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling GPMC Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: GPMC Clock Enabled (100MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling ELM Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: ELM Clock Enabled (50MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling MMCSD Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MMCSD Clock Enabled (48MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCSPI0 Clock Enabled (48MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCSPI1 Clock Enabled (48MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCSPI2 Clock Enabled (48MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCSPI3 Clock Enabled (48MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: MCSPI4 Clock Enabled (48MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: CONTROLSS Clock Enabled (400MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling CPTS Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: CPTS Clock Enabled (250MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: RGMII5 Clock Enabled (5MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: RGMII50 Clock Enabled (50MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: RGMII250 Clock Enabled (250MHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: TEMPSENSE Clock Enabled (32KHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: XTAL_MMC Clock Enabled (32KHz) [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: ***All IP Clocks are Enabled*** [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: AM2631 [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: Board Selected : CC [2025/9/19 上午10:52:00] [INFO] Cortex_R5_0: GEL Output: CPU reset (soft reset) has been issued through GEL on program load. [2025/9/19 上午10:52:02] [INFO] Cortex_R5_0: Writing 1 chunk at offset 0x0 [2025/9/19 上午10:52:22] [ERROR] Cortex_R5_0: Run failed... [2025/9/19 上午10:52:22] [ERROR] Cortex_R5_0: Trouble Removing Breakpoint with the Action "Remain Halted" at 0x70009310: (Error -1066 @ 0x70009310) Unable to set/clear requested breakpoint. Verify that the breakpoint address is in valid memory. (Emulation package 20.2.0.3575) [2025/9/19 上午10:52:22] [ERROR] Cortex_R5_0: File Loader: Memory write failed: Timed out waiting for target to halt while executing am263x_flasher.out [2025/9/19 上午10:52:23] [INFO] Cortex_R5_0: Writing 1 chunk at offset 0x0 ///////second flashing fail log [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched*** [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: AM263x Initialization Scripts Launched. Please Wait... [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: AM263x_Cryst_Clock_Loss_Status() Launched [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Crystal Clock present [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: AM263x_SOP_Mode() Launched [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: SOP MODE = 0x00000000 [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: QSPI - 4S Functional boot mode [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: AM263x_Read_Device_Type() Launched [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: AM263x_Check_supported_mode() Launched [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: The Device supports Lockstep mode [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: mode = 0 [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: *** R5FSS0 Lockstep Reset *** [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: *** R5FSS1 Lockstep Reset *** [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: R5F ROM Eclipse [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: R5FSS0_0 Released [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: R5FSS0_1 Released [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: R5FSS1_0 Released [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: R5FSS1_1 Released [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: All R5F Cores Released for program load [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: L2 Mem Init Complete [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MailBox Mem Init Complete [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: *********** R5FSS0/1 Lockstep mode Configured******** [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: CORE PLL Configuration Complete [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: SYS_CLK DIVBY2 [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: CLK Programmed R5F=400MHz and SYS_CLK=200MHz [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: *** Enabling Peripheral Clocks *** [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: RTI0 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: RTI1 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: RTI2 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: RTI3 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: WDT0 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: WDT1 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: WDT2 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: WDT3 Clock Enabled (200MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: LIN0_UART0 Clock Enabled (160MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: LIN1_UART1 Clock Enabled (160MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: LIN2_UART2 Clock Enabled (160MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: LIN3_UART3 Clock Enabled (160MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: LIN4_UART4 Clock Enabled (160MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: LIN5_UART5 Clock Enabled (160MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling QSPI Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: QSPI0 Clock Enabled (80MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling I2C Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: I2C Clock Enabled (48MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling TRACE Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Trace Clock Enabled (250MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCAN0 Clock Enabled (80MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCAN1 Clock Enabled (80MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCAN2 Clock Enabled (80MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCAN3 Clock Enabled (80MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling GPMC Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: GPMC Clock Enabled (100MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling ELM Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: ELM Clock Enabled (50MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling MMCSD Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MMCSD Clock Enabled (48MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCSPI0 Clock Enabled (48MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCSPI1 Clock Enabled (48MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCSPI2 Clock Enabled (48MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCSPI3 Clock Enabled (48MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: MCSPI4 Clock Enabled (48MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: CONTROLSS Clock Enabled (400MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling CPTS Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: CPTS Clock Enabled (250MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: RGMII5 Clock Enabled (5MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: RGMII50 Clock Enabled (50MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: RGMII250 Clock Enabled (250MHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: TEMPSENSE Clock Enabled (32KHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: XTAL_MMC Clock Enabled (32KHz) [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: ***All IP Clocks are Enabled*** [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: AM2631 [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: Board Selected : CC [2025/9/17 下午4:36:12] [INFO] Cortex_R5_0: GEL Output: CPU reset (soft reset) has been issued through GEL on program load. [2025/9/17 下午4:36:14] [INFO] Cortex_R5_0: Writing 1 chunk at offset 0x0 [2025/9/17 下午4:36:20] [INFO] Cortex_R5_0: Writing 1 chunk at offset 0xc0000 [2025/9/17 下午4:36:22] [SUCCESS] Program Load completed successfully. [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched*** [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: AM263x Initialization Scripts Launched. Please Wait... [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: AM263x_Cryst_Clock_Loss_Status() Launched [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: Crystal Clock present [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: AM263x_SOP_Mode() Launched [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: SOP MODE = 0x00000000 [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: QSPI - 4S Functional boot mode [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: AM263x_Read_Device_Type() Launched [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: AM263x_Check_supported_mode() Launched [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: The Device supports Lockstep mode [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: mode = 0 [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: *** R5FSS0 Lockstep Reset *** [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: *** R5FSS1 Lockstep Reset *** [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: R5F ROM Eclipse [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: R5FSS0_0 Released [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: R5FSS0_1 Released [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: R5FSS1_0 Released [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: R5FSS1_1 Released [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: All R5F Cores Released for program load [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: L2 Mem Init Complete [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: MailBox Mem Init Complete [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: *********** R5FSS0/1 Lockstep mode Configured******** [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: CORE PLL Configuration Complete [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: SYS_CLK DIVBY2 [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: CLK Programmed R5F=400MHz and SYS_CLK=200MHz [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: *** Enabling Peripheral Clocks *** [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: RTI0 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: RTI1 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: RTI2 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: RTI3 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: WDT0 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: WDT1 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: WDT2 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: WDT3 Clock Enabled (200MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: LIN0_UART0 Clock Enabled (160MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: LIN1_UART1 Clock Enabled (160MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: LIN2_UART2 Clock Enabled (160MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: LIN3_UART3 Clock Enabled (160MHz) [2025/9/17 下午4:50:07] [INFO] Cortex_R5_0: GEL Output: LIN4_UART4 Clock Enabled (160MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: LIN5_UART5 Clock Enabled (160MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling QSPI Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: QSPI0 Clock Enabled (80MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling I2C Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: I2C Clock Enabled (48MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling TRACE Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Trace Clock Enabled (250MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCAN0 Clock Enabled (80MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCAN1 Clock Enabled (80MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCAN2 Clock Enabled (80MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCAN3 Clock Enabled (80MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling GPMC Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: GPMC Clock Enabled (100MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling ELM Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: ELM Clock Enabled (50MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling MMCSD Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MMCSD Clock Enabled (48MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCSPI0 Clock Enabled (48MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCSPI1 Clock Enabled (48MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCSPI2 Clock Enabled (48MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCSPI3 Clock Enabled (48MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: MCSPI4 Clock Enabled (48MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: CONTROLSS Clock Enabled (400MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling CPTS Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: CPTS Clock Enabled (250MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: RGMII5 Clock Enabled (5MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: RGMII50 Clock Enabled (50MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: RGMII250 Clock Enabled (250MHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: TEMPSENSE Clock Enabled (32KHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: XTAL_MMC Clock Enabled (32KHz) [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: ***All IP Clocks are Enabled*** [2025/9/17 下午4:50:08] [INFO] Cortex_R5_0: GEL Output: CPU reset (soft reset) has been issued through GEL on program load. [2025/9/17 下午4:50:10] [INFO] Cortex_R5_0: Writing 1 chunk at offset 0x0 [2025/9/17 下午4:50:30] [ERROR] Cortex_R5_0: Run failed... [2025/9/17 下午4:50:30] [ERROR] Cortex_R5_0: Trouble Removing Breakpoint with the Action "Remain Halted" at 0x70009310: (Error -1066 @ 0x70009310) Unable to set/clear requested breakpoint. Verify that the breakpoint address is in valid memory. (Emulation package 20.2.0.3575) [2025/9/17 下午4:50:30] [ERROR] Cortex_R5_0: File Loader: Memory write failed: Timed out waiting for target to halt while executing am263x_flasher.out [2025/9/17 下午4:50:31] [INFO] Cortex_R5_0: Writing 1 chunk at offset 0x0 [2025/9/17 下午9:12:48] [ERROR] Cortex_R5_0: Error: (Error -261 @ 0x0) Invalid response was received from the XDS110. (Emulation package 20.2.0.3575) [2025/9/17 下午9:12:51] [ERROR] CS_DAP_0: Error: (Error -261 @ 0x0) Invalid response was received from the XDS110. (Emulation package 20.2.0.3575) [2025/9/17 下午9:12:51] [ERROR] CS_DAP_0: Error: (Error -122 @ 0x0) A bad parameter value was detected within a function. It is likely a problem with `SC_ARGS' in SMG_call(). (Emulation package 20.2.0.3575) [2025/9/17 下午9:12:51] [ERROR] CS_DAP_0: Error: (Error -261 @ 0x0) Invalid response was received from the XDS110. (Emulation package 20.2.0.3575) [2025/9/17 下午9:12:51] [ERROR] Cortex_R5_0: Unable to determine target status after 20 attempts [2025/9/17 下午9:12:51] [ERROR] CS_DAP_0: Unable to determine target status after 20 attempts [2025/9/17 下午9:12:51] [ERROR] Cortex_R5_0: Failed to remove the debug state from the target before disconnecting. There may still be breakpoint op-codes embedded in program memory. It is recommended that you reset the emulator before you connect and reload your program before you continue debugging [2025/9/17 下午9:12:51] [ERROR] CS_DAP_0: Failed to remove the debug state from the target before disconnecting. There may still be breakpoint op-codes embedded in program memory. It is recommended that you reset the emulator before you connect and reload your program before you continue debugging