Other Parts Discussed in Thread: TMDSCNCD263P

Tool/software:

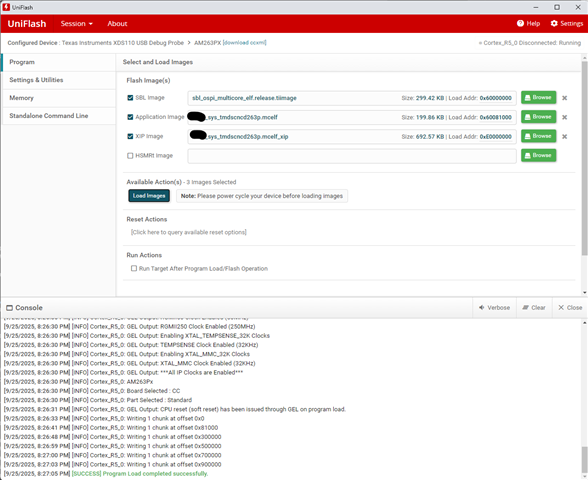

Using Uniflash 9.3.0.5401. TMDSCNCD263P Rev A.

Generated standalone command line package using onboard XDS110 to program SBL, mcelf and mcelf_xip images.

Works fine from the Uniflash GUI.

But when running dslite-Cortex_R5_0.bat from CLI it consistently fails trying to program mcelf_xip image using address 0xE000_0000.

PS C:\Work\uniflash_windows> .\dslite-Cortex_R5_0.bat

Executing default command:

> dslite --mode flash -c user_files/configs/AM263Px.ccxml -l user_files/settings/generated.ufsettings -s VerifyAfterProgramLoad="No verification" -e -f -v "user_files/images/sbl_ospi_multicore_elf.release.tiimage,0x60000000" "user_files/images/proj_sys_tmdscncd263p.mcelf,0x60081000" "user_files/images/proj_sys_tmdscncd263p.mcelf_xip,0xE0000000"

...

error: Cortex_R5_0: File Loader: Verification failed: Values at address 0xE0000000 do not match (expected: 0x7F, actual: 0xD0) Please verify target memory and memory map.

Finished: 41%

Failed: File: Multiple Files: a data verification error occurred, file load failed.

Here's the full log.

The same issue is seen when using appimage and address 0xF000_0000.

Is there a special step or command to program the XIP image? and why did the standalone command line package not generate the proper commands?

Thanks for the help.