Other Parts Discussed in Thread: TMDSCNCD263P, AM263P4, AM2634

Tool/software:

Using uniflash 9.2.0 and 9.3.0 on TMDSCNCD263P and BOOTMODE=OSPI(8s)

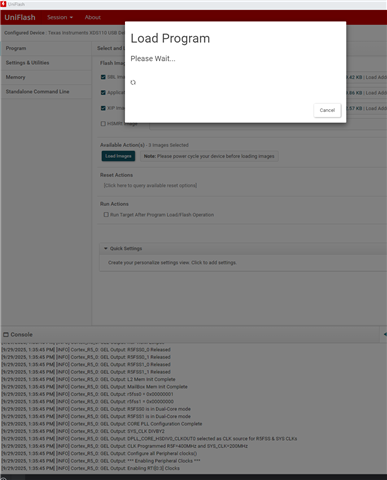

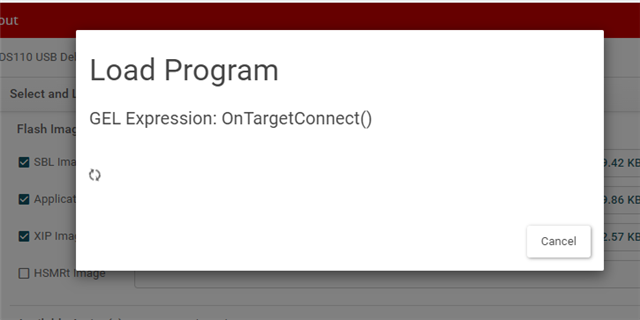

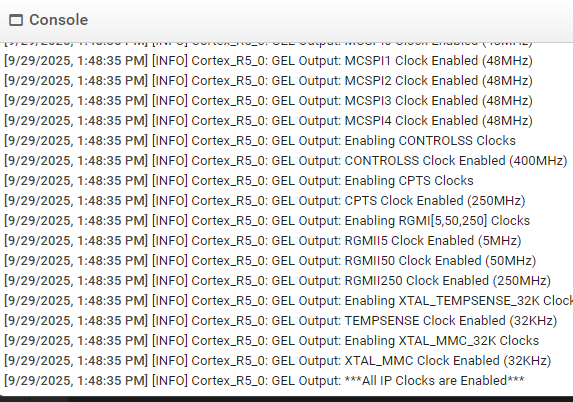

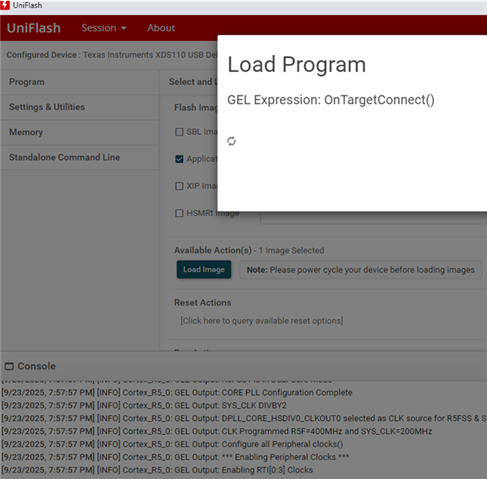

Uniflash tools keep hanging when it reaches:

"Enabling RTI[0:3]Clocks" and "GEL Expression: OnTargetConnect()"

I don't have the exact sequence to replicate this, but switching applications, switching between 9.2 and 9.3, computer going to sleep may have something to do with it.

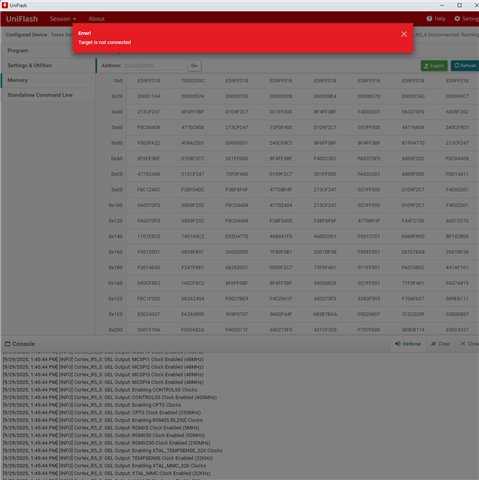

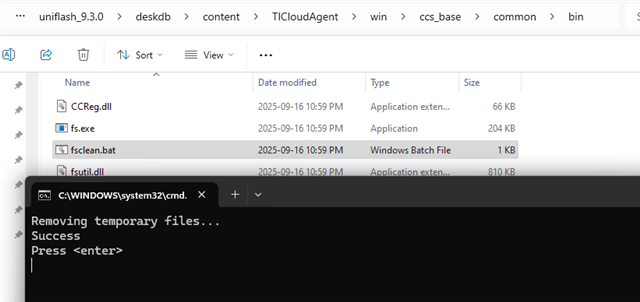

Once it gets into this state, it will stay in this state unless I close the tool and run fsclean.bat. And even this sometimes needs to be done several times. Including disconnect the USB cable to XDS110 sometimes.

I've tried reinstalling both versions.

How can I make this experience better for the team. Seems people are seeing this quite often and are getting very frustrated with having to restart and reselect the files.

And when we are using on a remote machine, it is not convenient to pull the debug cable.

Any help to improve this is appreciated.