Tool/software:

Hello,

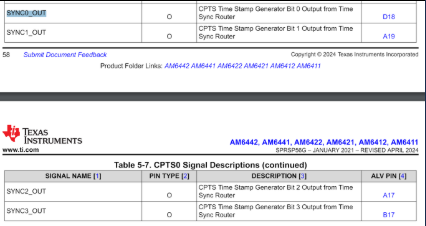

is it possible to remap the SYNC0_OUT signal to another pin?

In the PN example (pn_app_iod_bsp.c), it is mapped to Ball.D18:

/*

* PAD configuration for Ball.D18

* Required to configure SYNC0_OUT as pin out

*/

static Pinmux_PerCfg_t gTsrPinMuxMainDomainCfg[] = {

{

PIN_ECAP0_IN_APWM_OUT,

( PIN_MODE(1) | PIN_PULL_DISABLE ) /* PIN_MODE 1 is SYNC0_OUT */

},

{PINMUX_END, PINMUX_END}

};

void PN_APP_IOD_tsrConfig(uint8_t syncSignal)

{

Pinmux_config(gTsrPinMuxMainDomainCfg, PINMUX_DOMAIN_ID_MAIN);

/* PRU IEP Enable SYNC MODE */

CSL_REG32_WR(CSL_PRU_ICSSG1_PR1_CFG_SLV_BASE + CSL_ICSSCFG_IEPCLK, 1);

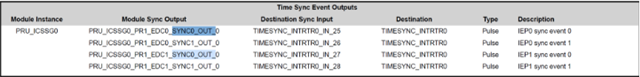

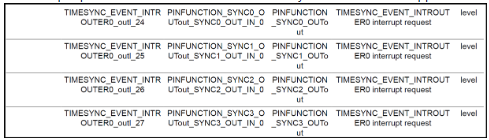

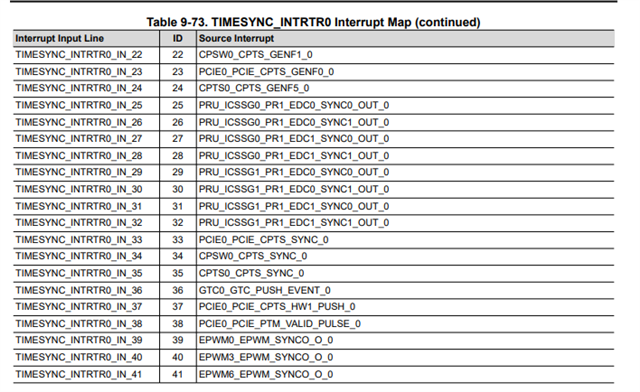

CSL_REG32_WR(CSL_TIMESYNC_EVENT_INTROUTER0_CFG_BASE + 0x64, 0x0001001D + syncSignal);

}

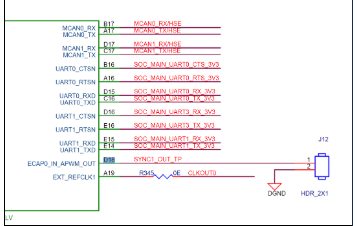

Ideally to Ball.B16 (UART0_CTS_N)?

I tried to find information in the Technical Reference Manual, but I am confused.

Regards,

Vaclav