Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN,

Tool/software:

Hi at all,

I refer to forum entry TMS570LC4357: Data abort when run code in Ram - Arm-based microcontrollers forum - Arm-based microcontrollers - TI E2E support forums where this problem was already discussed but sadly not solved.

I have got also the issue that when moving a too large amount of code to RAM, an exception occurs after a view cycles. Following settings were made:

HalCoGen:

The RAM is prepared for execution of Code.

The function Scheduler_L4 is started from a Software Interrupt and is located into the RAM area.

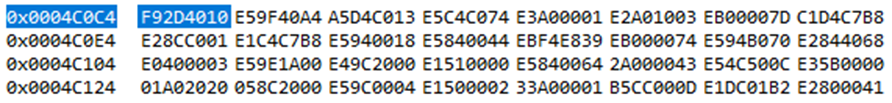

This is the first instruction of the function which means undefined op code. When moving with Assembly steps, a jump is done to address 0x00000004 where nothing reasonable is defined. Then the undef exception occurs.

My functions for copying from flash to RAM have a size of 0x57ac.

The area of RAM is not violated. 0x806d4e0 + 0x57ac = 0x8072C8C which is a valid address within MPU region 3.

When copying only 0x3504 Bytes of code, everything is working fine.

Then the first instruction of function Scheduler_L4() looks as follows:

So, the instruction changed from 0xE92D4010 to 0xF92D4010.

Further information: Cache is enabled and the complete code which is copied to RAM is called within the Software Interrupt ISR.

Can you please help me, why there is this obvious dependency with the size of code copied to RAM to the changed instruction in one of the functions…

All the settings (HALCOGEN, linker file) are unchanged, only the size of code changed.

Thanks,

Christian