Part Number: MSPM0C1106

Other Parts Discussed in Thread: MSPM0C1105

Hello,

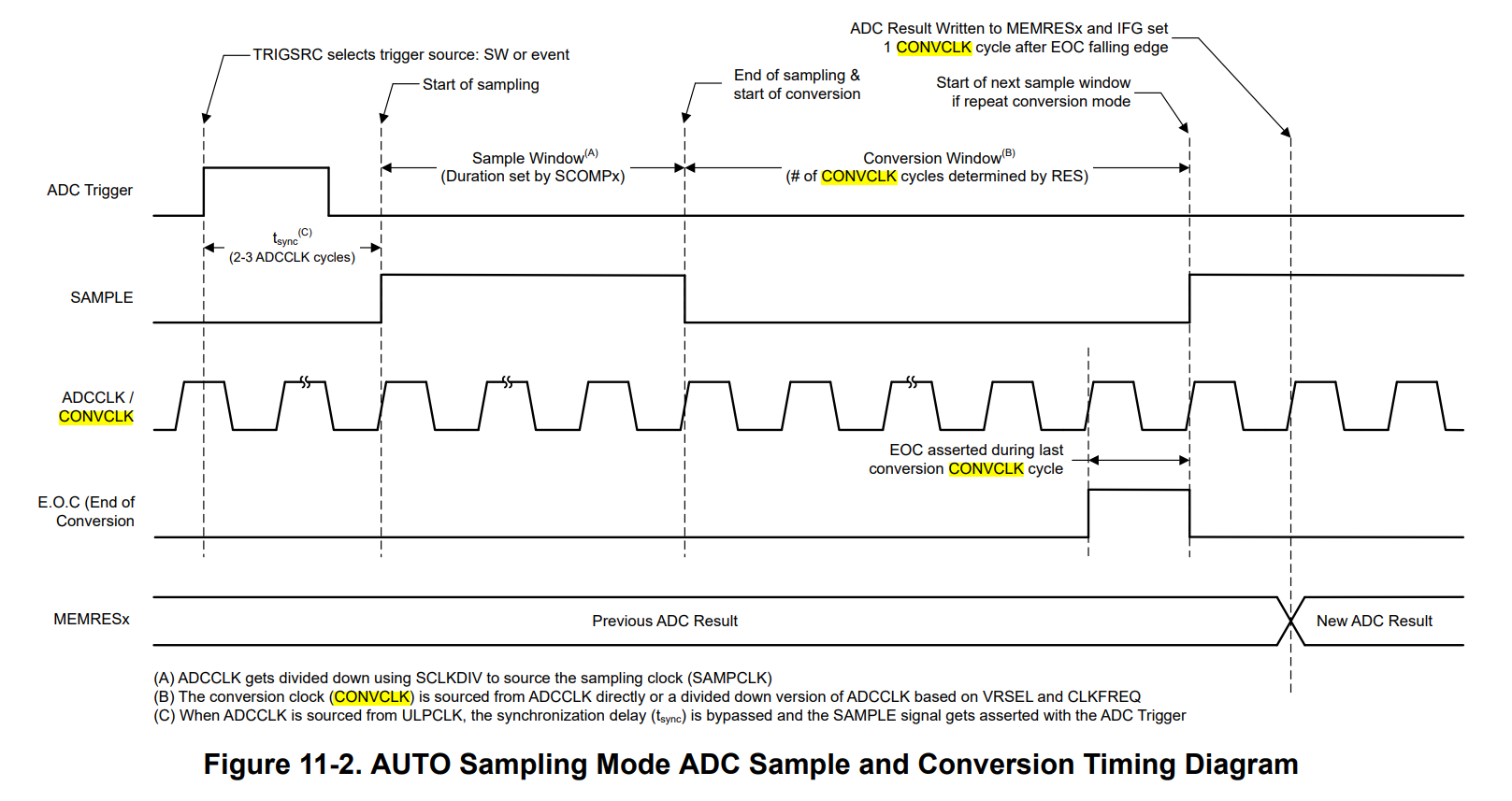

Just so I'm clear on the topic, from this diagram in the TRM:

On MSPM0C1106 there is no independent adc oscillator correct? So ADCCLK is either ULPCLK or one of the other system clocks?

However for SAMPCLK this can be ADCCLK/ SCLKDIV and this is considered an entirely different clock just for timing the ADC sampling correct?

So sampling occurs for SCOMP0/1 counts of SAMPCLK and then the rest of the ADC conversion happens at ADCCLK?

This diagram doesn't really make that clear, there should be another line for sample clock to deliniate the difference if my understanding is correct.

Finally for what it's worth, I noticed that the MSPM0C TRM still references a 24 MHz max clock speed, shouldn't this now be 32 MHz given that the MSPM0C1106 is 32 MHz?

Munan