Hello,

I want to preface this with - I am using freeRTOS to manage multiple tasks. I have a dedicated task for communicating with an external IC.

I am working on a project which uses the UART peripheral to communicate with an external IC periodically. I have created a UART driver to use with my application. The driver was created referencing the uart_rx_multibyte_fifo_dma_interrupt example project. With the driver working, I am now trying to ensure any issues with the code can be caught and an appropriate action can be done to handle the issue.

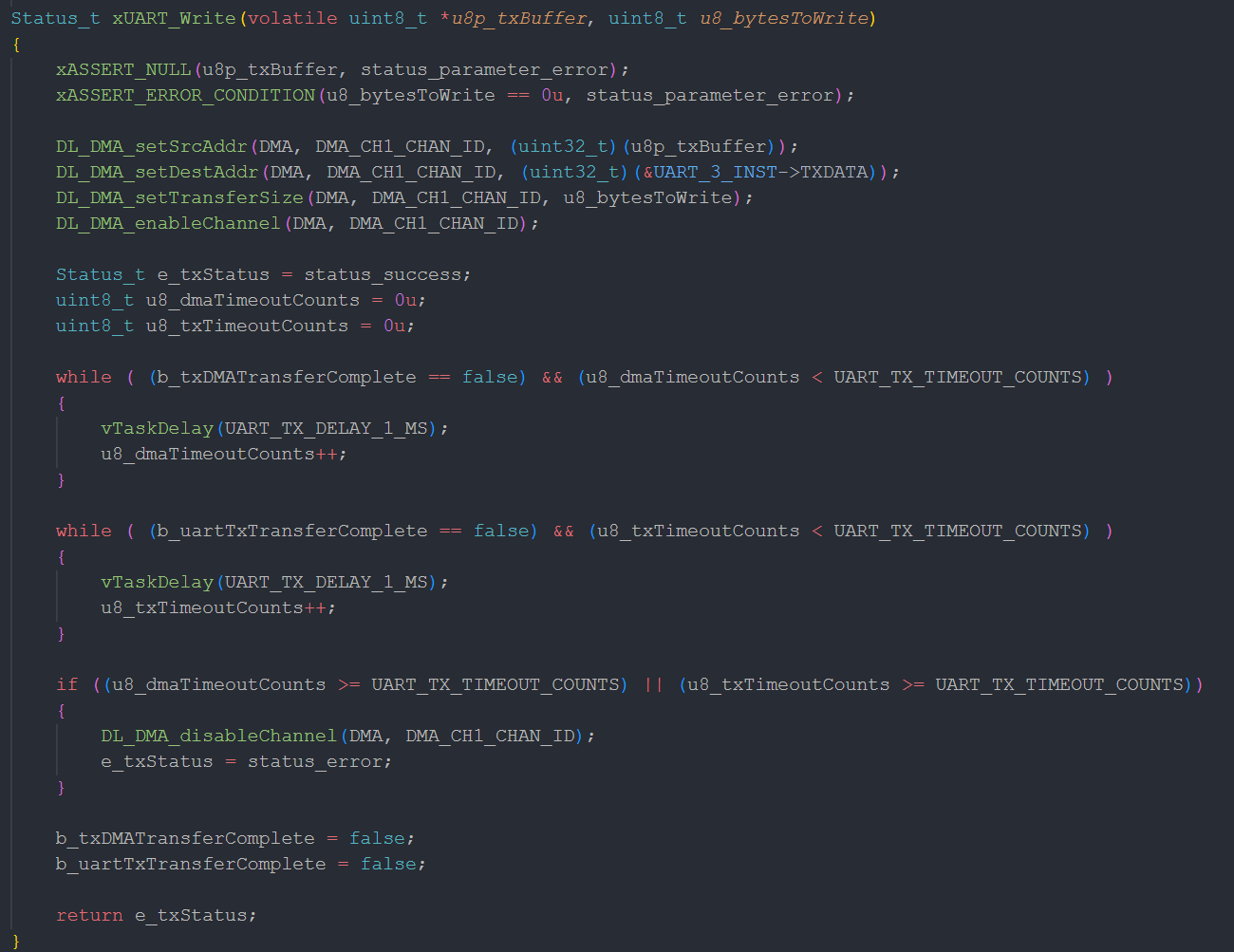

For example, below is a screenshot of my write function.

When initiating a write, the software needs to wait for the DMA to move all data bytes into the UART TX FIFO and then it waits for the UART peripheral to finish outputting the data on the bus. These two areas can (in theory) fail. To mitigate this, I have added a timeout to each while loop. I have measured the time it takes for the DMA and TX UART to finish. It takes the chip ~223us to trigger the DMA done and UART done interrupts. Therefore, I have set a timeout of ~3ms.

So my question is: if somehow the TX DMA never triggers and/or the UART somehow doesn't finish transmitting the data, what should be the corrective action that should occur. Right now, I am just disabling the TX DMA channel. Is this sufficient? Also, is there a way to get the software to trigger these error, so I can fully test the behavior?

On the same note, now on the receiving end, below is a screenshot of the error handling I am doing.

For this function, if the RX DMA does not receive it's transfer size within ~30ms I timeout. The corrective action I am doing here is basically disable the RX DMA and clear the RX FIFO. This one seems a bit more straight-forward and I think, for the following events, this is sufficient.

- No data bytes were received

- Partial data bytes were received

- Overrun of bytes were received

So for this one, I just ask if this is good enough.

Thanks,

Adan Pantoja