Part Number: AM2612-Q1

Hi experts,

Good day! I am asking for customer.

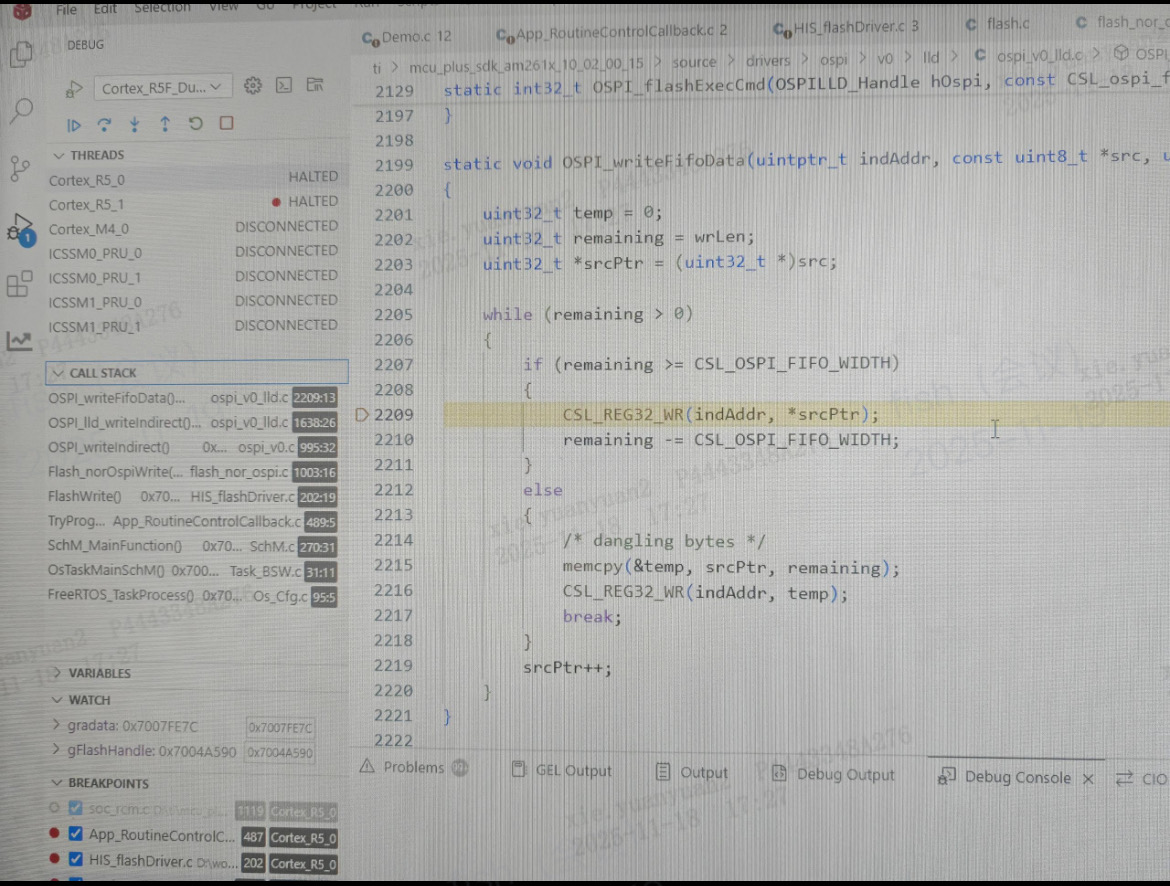

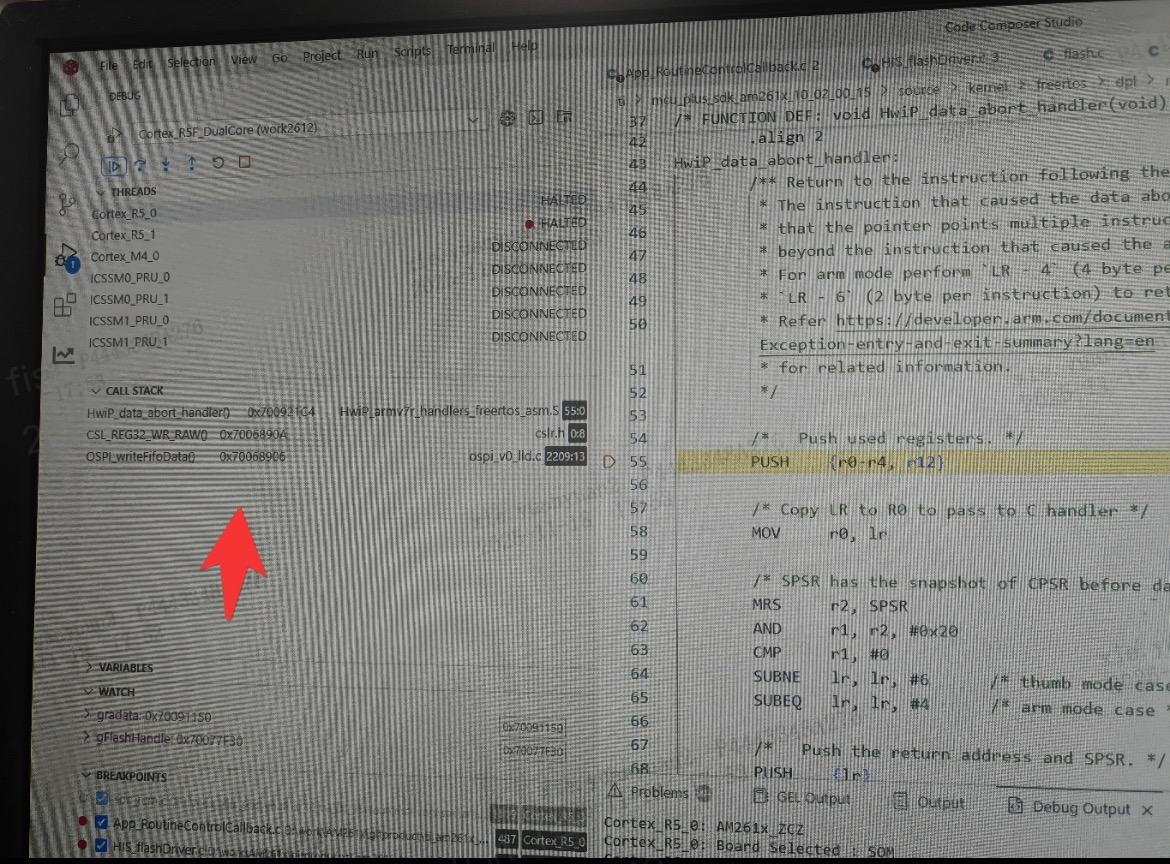

My customer is developing AM261 with their own board. They will call function function OSPI_writeFifoData() int their code. They found that when they build the code with build configuration "debug", it can operate flash well when debug the code. But when they build the code with build configuration "release", the CPU will jump to Hwip_data_abort_handler.

Before jumping to Hwip_data_abort_handler, it runs on CSL_REG32_WR(indAddr, *srcPtr). This issue will occurs on address 0x880000, length is 256 bytes.

Could you help to check what will cause the CPU jumps to Hwip_data_abort_handler when execute OSPI_writeFifoData()? What's difference between "release" and "debug" on function OSPI_writeFifoData()

Best Regards

Kita