Part Number: AM2634-Q1

Other Parts Discussed in Thread: AM2634

Hi TI team,

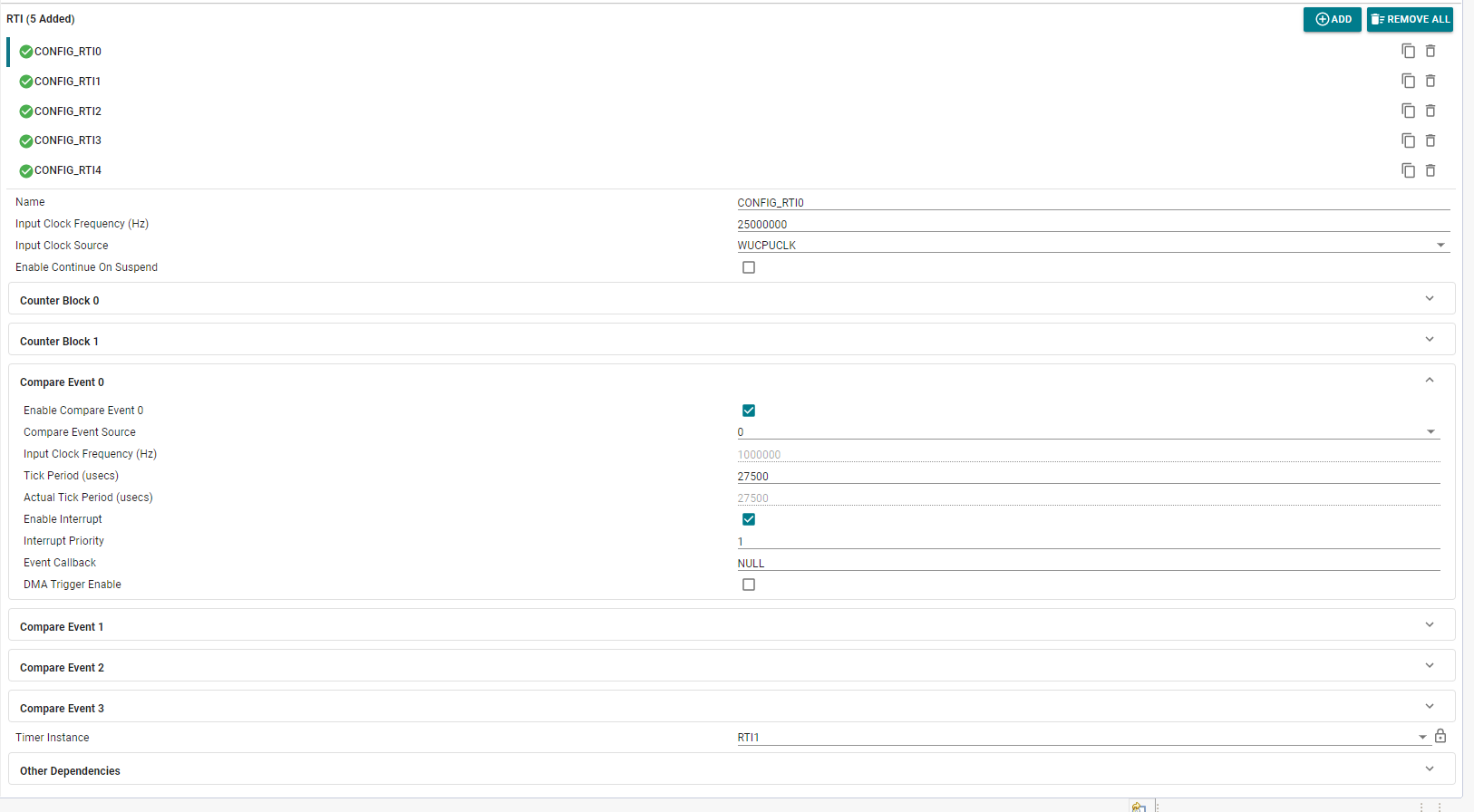

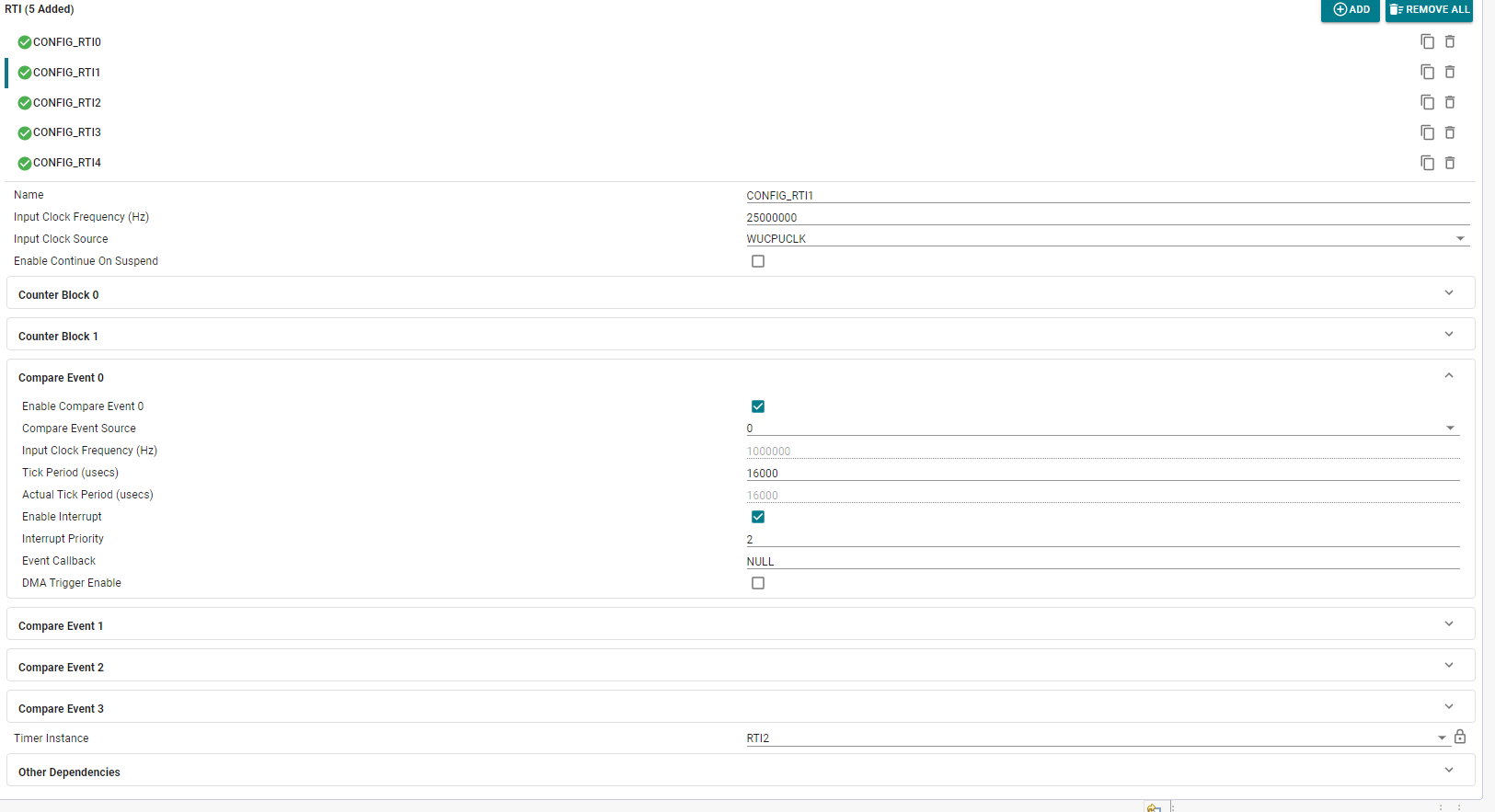

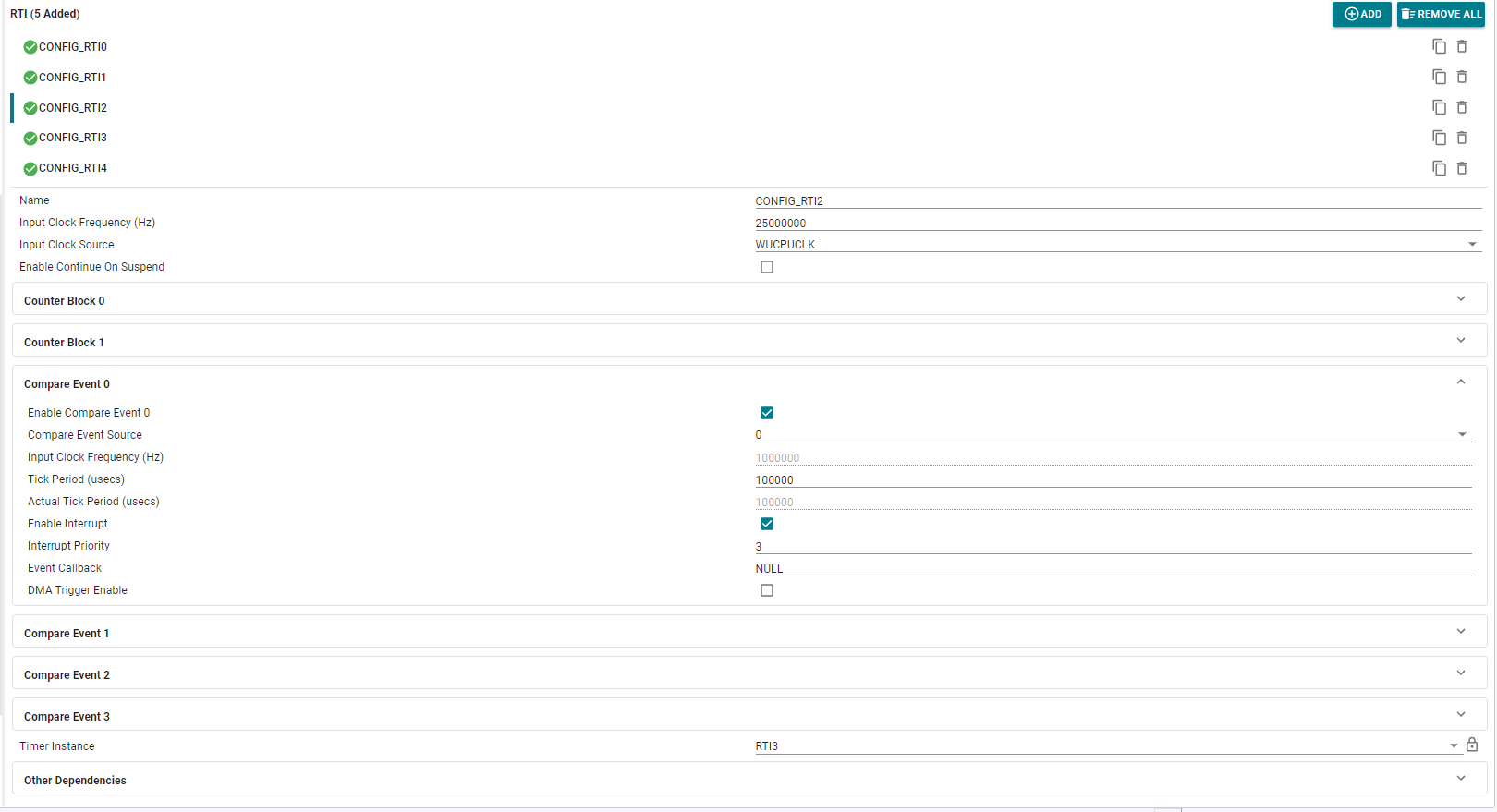

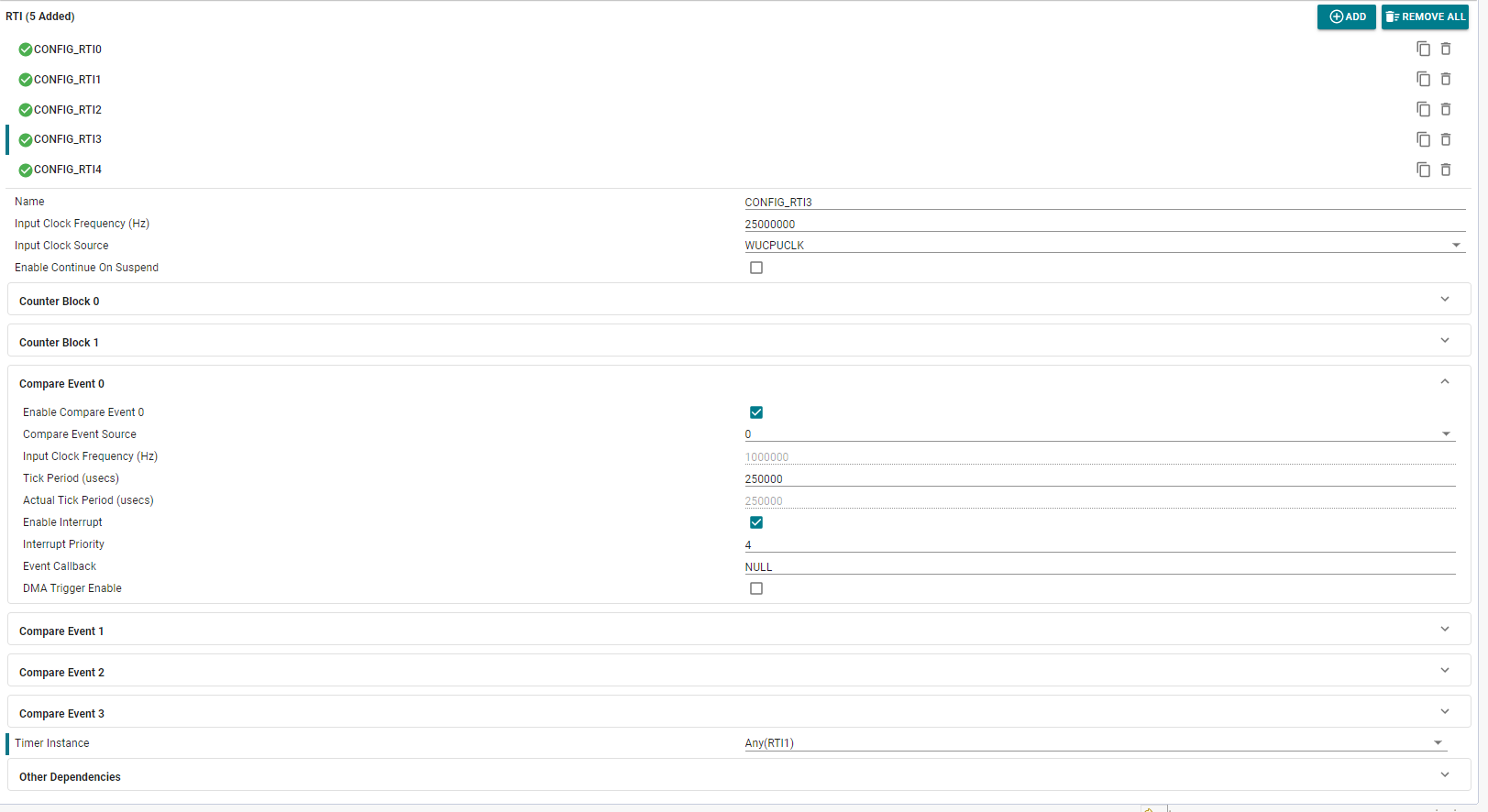

as per our requirement we need 5 type of timers, previousely we used RTI0 with 4 comparators and RTI1 with 1 comparator. but now we planned to use RTI0, RTI1,RTI2,RTI3,RTI4 (1 comparator).

Issuses:

- RTI0_isr() and RTI4_isr() only enabling and other timers are not enabling.

- we open the RTI channels, enable the RTI timers. Even though we could not able to create the interrupt on RTI1_isr(), RTI2_isr() and RTI3_isr().

- Is that possible to use different RTI timers?

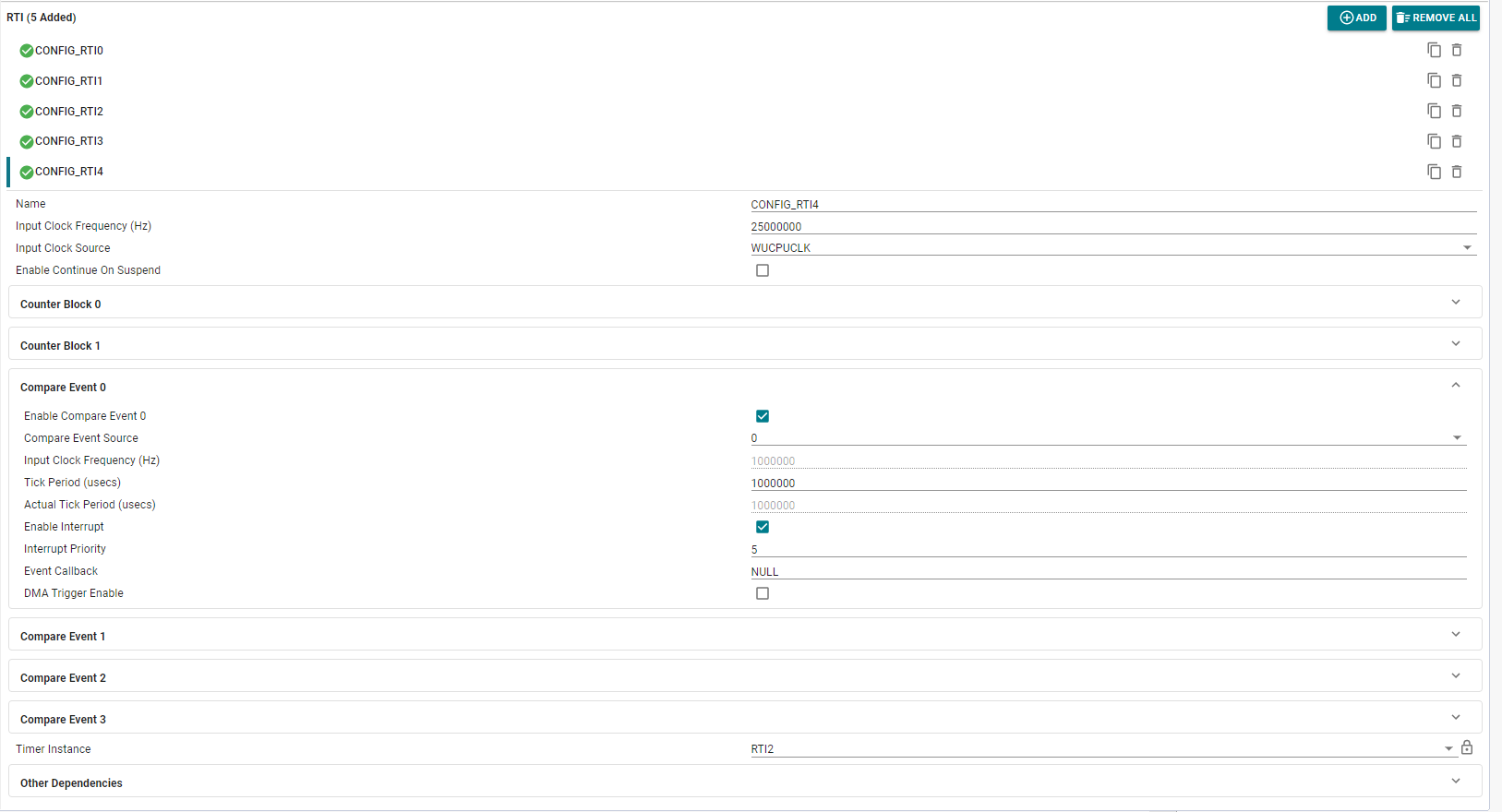

herewith attached the config as below,

these are the above configuration done and we have got below code which generated by the CCS,

void Drivers_rtiOpen(void)

{

HwiP_Params rtiHwiParams;

int32_t status;

uint32_t baseAddr;

uint64_t timeInNsec;

uint32_t cntrPrescaler;

uint32_t compPrescaler;

baseAddr = CONFIG_RTI0_BASE_ADDR;

/* Configure RTI input clock source */

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_RTI0_CLOCK_SRC_MUX_ADDR) = CONFIG_RTI0_CLOCK_SRC_WUCPUCLK;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

/* Enable/Disable Continue on Suspend */

RTIG_setStallMode(baseAddr, RTI_GC_STALL_MODE_OFF);

/* Configure Compare event 0 */

timeInNsec = CONFIG_RTI0_NSEC_PER_TICK_COMP0;

if(timeInNsec == 0)

{

timeInNsec = CONFIG_RTI0_USEC_PER_TICK_COMP0 * 1000U;

}

compPrescaler = (timeInNsec*CONFIG_RTI0_COMP0_INPUT_CLK_HZ)/1000000000;

RTI_compareEventConfig(baseAddr, RTI_TMR_CMP_BLK_INDEX_0, CONFIG_RTI0_COMP0_SRC, compPrescaler, compPrescaler);

RTI_intStatusClear(baseAddr, RTI_TMR_INT_INT0_FLAG);

HwiP_Params_init(&rtiHwiParams);

rtiHwiParams.intNum = CONFIG_RTI0_INT_NUM_EVENT0;

rtiHwiParams.callback = RTI0_event0Isr;

rtiHwiParams.isPulse = 0;

rtiHwiParams.priority = 1;

status = HwiP_construct(&gRtiEvent0HwiObj[CONFIG_RTI0], &rtiHwiParams);

DebugP_assertNoLog(status==SystemP_SUCCESS);

RTI_intEnable(baseAddr, RTI_TMR_INT_INT0_FLAG);

RTI_intDisable(baseAddr, RTI_TMR_INT_DMA0_FLAG);

baseAddr = CONFIG_RTI1_BASE_ADDR;

/* Configure RTI input clock source */

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_RTI1_CLOCK_SRC_MUX_ADDR) = CONFIG_RTI1_CLOCK_SRC_WUCPUCLK;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

/* Enable/Disable Continue on Suspend */

RTIG_setStallMode(baseAddr, RTI_GC_STALL_MODE_OFF);

/* Configure Compare event 0 */

timeInNsec = CONFIG_RTI1_NSEC_PER_TICK_COMP0;

if(timeInNsec == 0)

{

timeInNsec = CONFIG_RTI1_USEC_PER_TICK_COMP0 * 1000U;

}

compPrescaler = (timeInNsec*CONFIG_RTI1_COMP0_INPUT_CLK_HZ)/1000000000;

RTI_compareEventConfig(baseAddr, RTI_TMR_CMP_BLK_INDEX_0, CONFIG_RTI1_COMP0_SRC, compPrescaler, compPrescaler);

RTI_intStatusClear(baseAddr, RTI_TMR_INT_INT0_FLAG);

HwiP_Params_init(&rtiHwiParams);

rtiHwiParams.intNum = CONFIG_RTI1_INT_NUM_EVENT0;

rtiHwiParams.callback = RTI1_event0Isr;

rtiHwiParams.isPulse = 0;

rtiHwiParams.priority = 2;

status = HwiP_construct(&gRtiEvent0HwiObj[CONFIG_RTI1], &rtiHwiParams);

DebugP_assertNoLog(status==SystemP_SUCCESS);

RTI_intEnable(baseAddr, RTI_TMR_INT_INT0_FLAG);

RTI_intDisable(baseAddr, RTI_TMR_INT_DMA0_FLAG);

baseAddr = CONFIG_RTI2_BASE_ADDR;

/* Configure RTI input clock source */

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_RTI2_CLOCK_SRC_MUX_ADDR) = CONFIG_RTI2_CLOCK_SRC_WUCPUCLK;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

/* Enable/Disable Continue on Suspend */

RTIG_setStallMode(baseAddr, RTI_GC_STALL_MODE_OFF);

/* Configure Compare event 0 */

timeInNsec = CONFIG_RTI2_NSEC_PER_TICK_COMP0;

if(timeInNsec == 0)

{

timeInNsec = CONFIG_RTI2_USEC_PER_TICK_COMP0 * 1000U;

}

compPrescaler = (timeInNsec*CONFIG_RTI2_COMP0_INPUT_CLK_HZ)/1000000000;

RTI_compareEventConfig(baseAddr, RTI_TMR_CMP_BLK_INDEX_0, CONFIG_RTI2_COMP0_SRC, compPrescaler, compPrescaler);

RTI_intStatusClear(baseAddr, RTI_TMR_INT_INT0_FLAG);

HwiP_Params_init(&rtiHwiParams);

rtiHwiParams.intNum = CONFIG_RTI2_INT_NUM_EVENT0;

rtiHwiParams.callback = RTI2_event0Isr;

rtiHwiParams.isPulse = 0;

rtiHwiParams.priority = 3;

status = HwiP_construct(&gRtiEvent0HwiObj[CONFIG_RTI2], &rtiHwiParams);

DebugP_assertNoLog(status==SystemP_SUCCESS);

RTI_intEnable(baseAddr, RTI_TMR_INT_INT0_FLAG);

RTI_intDisable(baseAddr, RTI_TMR_INT_DMA0_FLAG);

baseAddr = CONFIG_RTI3_BASE_ADDR;

/* Configure RTI input clock source */

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_RTI3_CLOCK_SRC_MUX_ADDR) = CONFIG_RTI3_CLOCK_SRC_WUCPUCLK;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

/* Enable/Disable Continue on Suspend */

RTIG_setStallMode(baseAddr, RTI_GC_STALL_MODE_OFF);

/* Configure Compare event 0 */

timeInNsec = CONFIG_RTI3_NSEC_PER_TICK_COMP0;

if(timeInNsec == 0)

{

timeInNsec = CONFIG_RTI3_USEC_PER_TICK_COMP0 * 1000U;

}

compPrescaler = (timeInNsec*CONFIG_RTI3_COMP0_INPUT_CLK_HZ)/1000000000;

RTI_compareEventConfig(baseAddr, RTI_TMR_CMP_BLK_INDEX_0, CONFIG_RTI3_COMP0_SRC, compPrescaler, compPrescaler);

RTI_intStatusClear(baseAddr, RTI_TMR_INT_INT0_FLAG);

HwiP_Params_init(&rtiHwiParams);

rtiHwiParams.intNum = CONFIG_RTI3_INT_NUM_EVENT0;

rtiHwiParams.callback = RTI3_event0Isr;

rtiHwiParams.isPulse = 0;

rtiHwiParams.priority = 4;

status = HwiP_construct(&gRtiEvent0HwiObj[CONFIG_RTI3], &rtiHwiParams);

DebugP_assertNoLog(status==SystemP_SUCCESS);

RTI_intEnable(baseAddr, RTI_TMR_INT_INT0_FLAG);

RTI_intDisable(baseAddr, RTI_TMR_INT_DMA0_FLAG);

baseAddr = CONFIG_RTI4_BASE_ADDR;

/* Configure RTI input clock source */

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_RTI4_CLOCK_SRC_MUX_ADDR) = CONFIG_RTI4_CLOCK_SRC_WUCPUCLK;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, MSS_RCM_PARTITION0);

/* Enable/Disable Continue on Suspend */

RTIG_setStallMode(baseAddr, RTI_GC_STALL_MODE_OFF);

/* Configure Compare event 0 */

timeInNsec = CONFIG_RTI4_NSEC_PER_TICK_COMP0;

if(timeInNsec == 0)

{

timeInNsec = CONFIG_RTI4_USEC_PER_TICK_COMP0 * 1000U;

}

compPrescaler = (timeInNsec*CONFIG_RTI4_COMP0_INPUT_CLK_HZ)/1000000000;

RTI_compareEventConfig(baseAddr, RTI_TMR_CMP_BLK_INDEX_0, CONFIG_RTI4_COMP0_SRC, compPrescaler, compPrescaler);

RTI_intStatusClear(baseAddr, RTI_TMR_INT_INT0_FLAG);

HwiP_Params_init(&rtiHwiParams);

rtiHwiParams.intNum = CONFIG_RTI4_INT_NUM_EVENT0;

rtiHwiParams.callback = RTI4_event0Isr;

rtiHwiParams.isPulse = 0;

rtiHwiParams.priority = 5;

status = HwiP_construct(&gRtiEvent0HwiObj[CONFIG_RTI4], &rtiHwiParams);

DebugP_assertNoLog(status==SystemP_SUCCESS);

RTI_intEnable(baseAddr, RTI_TMR_INT_INT0_FLAG);

RTI_intDisable(baseAddr, RTI_TMR_INT_DMA0_FLAG);

}

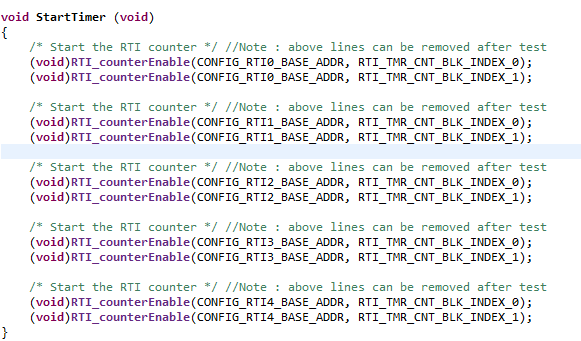

and we are enable the RTI timers as below,

here are the things have done in the code, but not working, can anyone guide in this?

thanks,

karthikeyan.S

Here.

Here.