Part Number: MSPM0L1117

Hello all,

I hope this mail find you good.

In the description "SLAU847E," it is stated that each microcontroller has 32 device-specific interrupts, which can include grouped interrupts.

However, I could not find any information about how many of these specific interrupts can actually be grouped.

I assume there could be up to 32 grouped interrupts, as the microcontroller's specific documentation (doc.MSPM0L1117 - SLASFC9, pages 50-51) describes interrupts such as DMA0, RTC_B, AESADV, etc., which are placed in the last interrupt slots.

Additional Information:

We are using IAR v9.6 (recommended by the SDK for this microcontroller family).

Here are my questions:

-

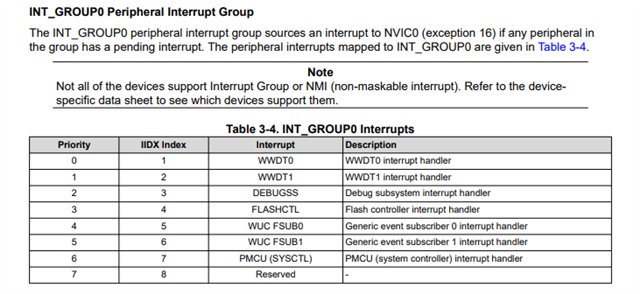

How many interrupt groups can the MSPM0L family support?

1.1. The ADC0 interrupt is defined as group 4 but does not have an assigned index. In this case, what value will the IIDX register return during an interrupt? The same question applies to other interrupts that have a "-" as their index. -

The DMA0 interrupt is assigned to interrupt 31 of the device-specific interrupts for the family (ref: MSPM0L1117 - SLASFC9, page 51). However, the CPUSS Registers for group 31 do not exist (ref: SLAU847E, pages 375-376). The question is: how can I enable, clear the interrupt flag, etc., since such a group of registers is missing?