Part Number: TMDS273EVM

Hello TI masters,

Im using the TMDS273EVM and my goal is to evaluate the LVDS interface by sending some buffers and monitor the signals with an oscilloscope.

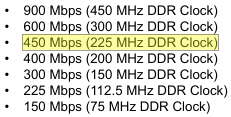

Using the default example, i see that 2 lanes are selected and the configuration is 450 Mbps (225 MHz DDR Clock) by measuring the LVDS CLK_P and aligning it with the supported values from the TRM (SPRUIU0E):

The example driver configures the HSI clock:

/* Configure HSI interface Clock */

HW_WR_REG32(CSL_MSS_TOPRCM_U_BASE + CSL_MSS_TOPRCM_HSI_CLK_SRC_SEL, 0x222);

HW_WR_REG32(CSL_MSS_TOPRCM_U_BASE + CSL_MSS_TOPRCM_HSI_DIV_VAL, 0x333);

Here i need your help to interpret this right in order to use the other supported modes and data rates:

By navigating through the TRM and the clock architecture, i see that this utilizes the the Clock Source: PLL_DSP_CLK (0x222 -> 2):

The clock divider is 0x333->3:

- I cannot see a divider value 3 in this table, am i missing something?

- How the 225Mhz clock is generated with these settings (Source: 2, Divider:3)?

- I want to send multiple buffers sequentially, but when i activate/deactivate session in a loop, the code does not run as expected (only when i re-run the example again), so what is the best practice with this driver to treat continuous data streams?

Thanks in advance,

Konstantinos