Part Number: TMS570LS0914

Project description:

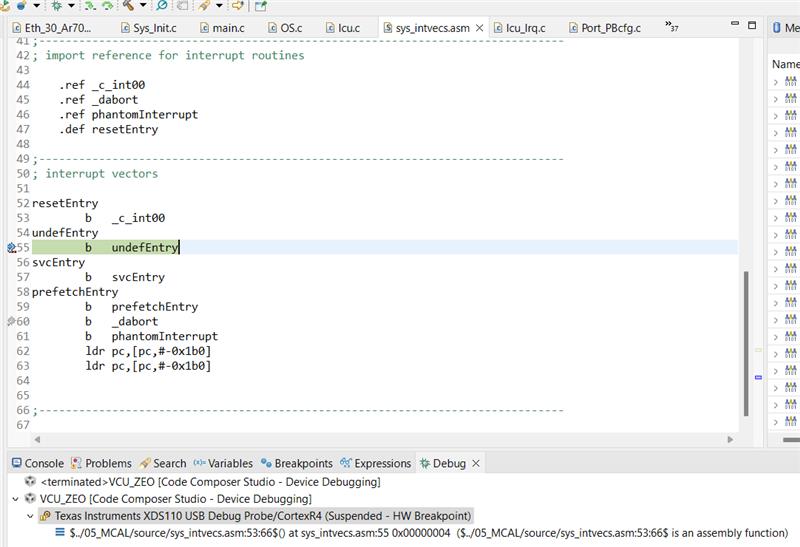

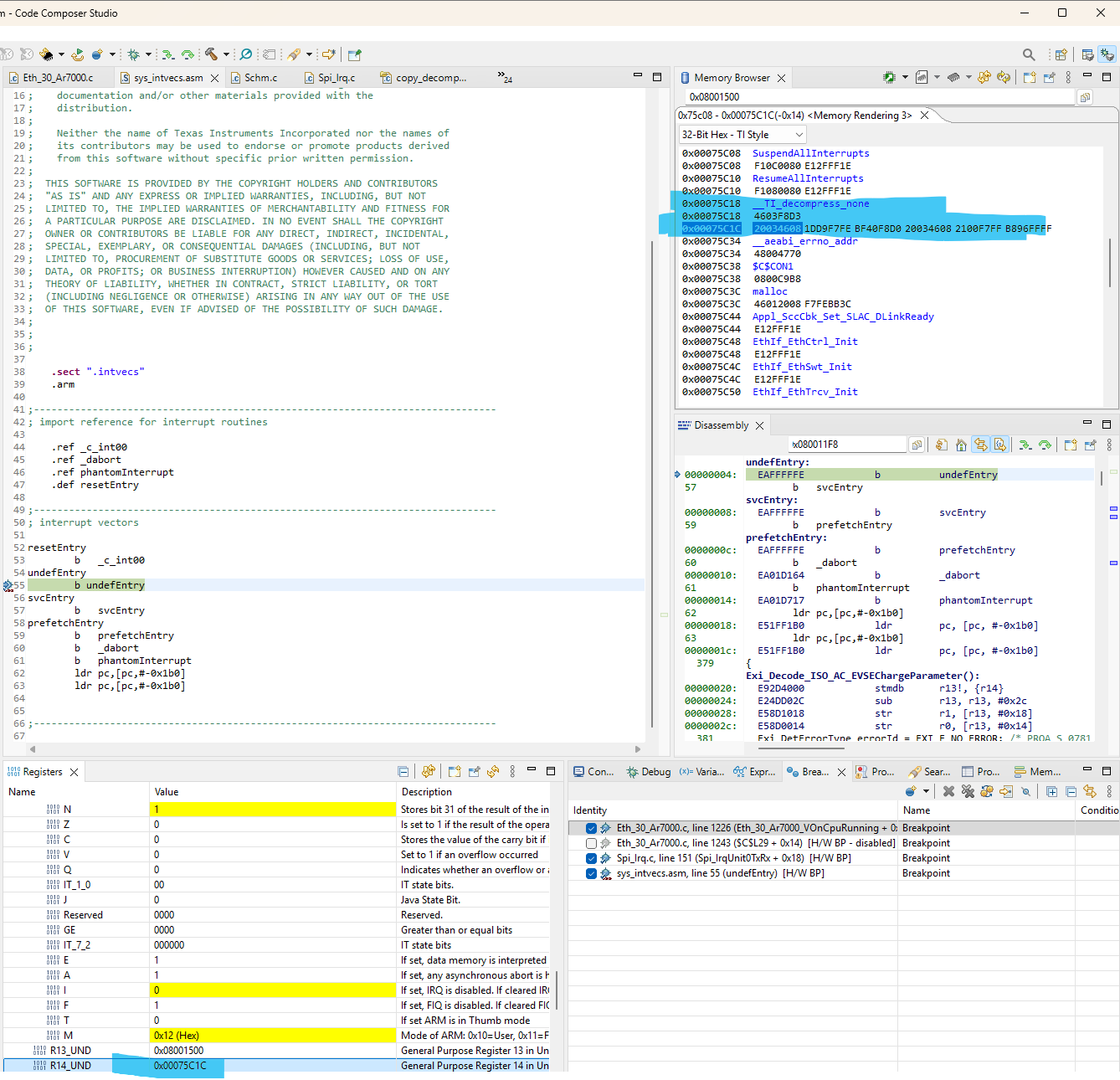

Trying to push firmware data from host(TMS570LS0914) to PLC chip (QCA7006) via SPI1. After excution of some commands it is going to undefEntry.

The LR is consistently pointing to this __TI_Decompress_None when the undefEntry is reached.

This issue is impacting the project flow, and resolving it will help us proceed to the firmware download activity for the PLC chip.