Part Number: AM2634

Other Parts Discussed in Thread: DP83826I

Hi expert,

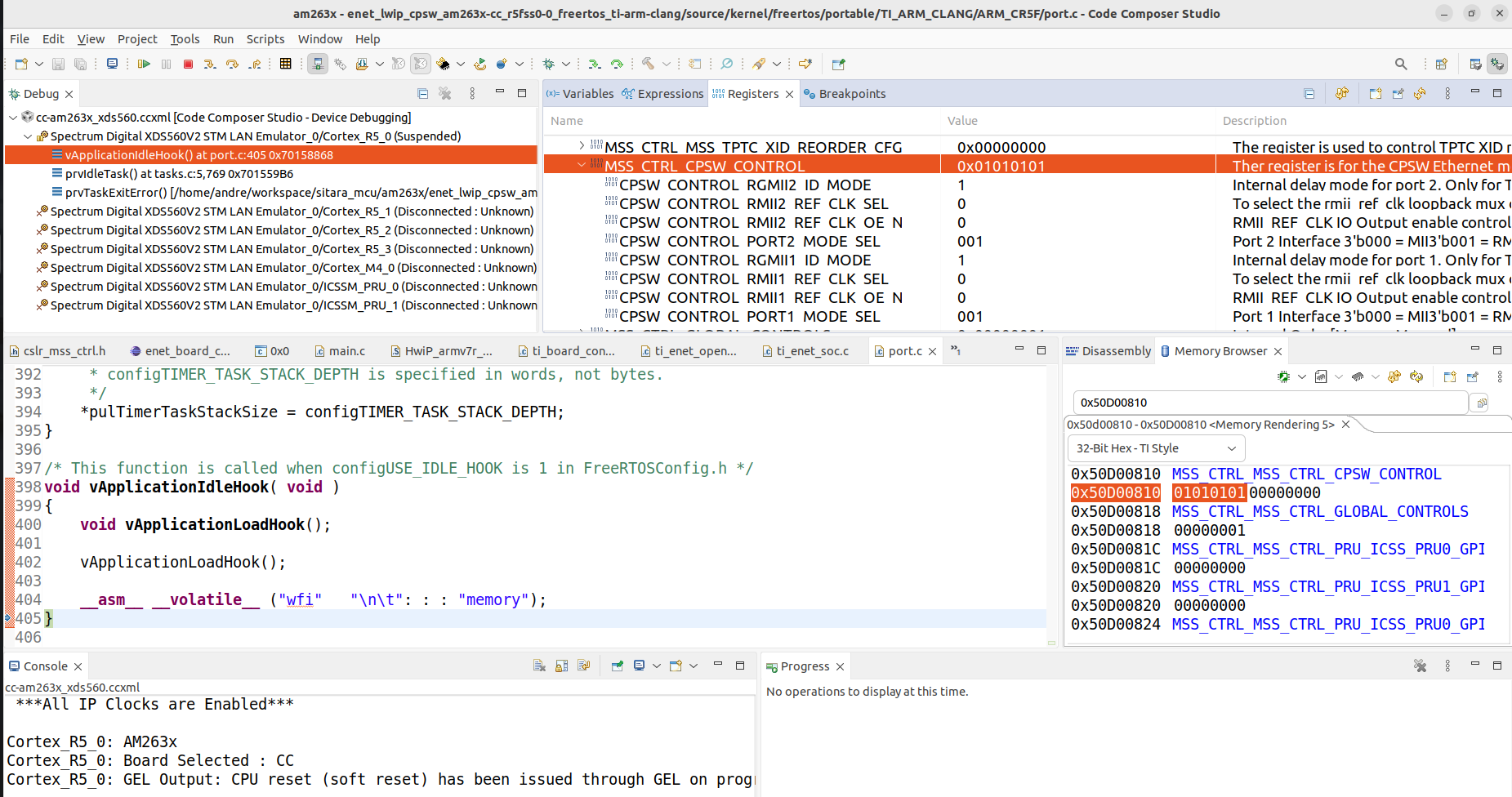

My customer is trying to use DP83826I with CPSW3G RMII interface on AM2634. During the test, we found 50 MHz RMII1_REF_CLK on R17 port are missing. We check the ti_board_config.c generated by syscfg, the API

int32_t EnetBoard_setupPorts(EnetBoard_EthPort *ethPorts,

uint32_t numEthPorts)

{

CSL_mss_ctrlRegs *mssCtrlRegs = (CSL_mss_ctrlRegs *)CSL_MSS_CTRL_U_BASE;

DebugP_assert(numEthPorts == 1);

EnetBoard_enableExternalMux();

switch(ethPorts->macPort)

{

case ENET_MAC_PORT_1:

CSL_FINS( mssCtrlRegs->CPSW_CONTROL,MSS_CTRL_CPSW_CONTROL_PORT1_MODE_SEL, MSS_CPSW_CONTROL_PORT_MODE_RMII);

break;

case ENET_MAC_PORT_2:

CSL_FINS( mssCtrlRegs->CPSW_CONTROL,MSS_CTRL_CPSW_CONTROL_PORT2_MODE_SEL, MSS_CPSW_CONTROL_PORT_MODE_RMII);

break;

default:

DebugP_assert(false);

}

/* Nothing else to do */

return ENET_SOK;

}

oad program and and verify register MSS_CTRL_CPSW_CONTROL = 0x01010101. This vale is not changed after this API called in all test period.

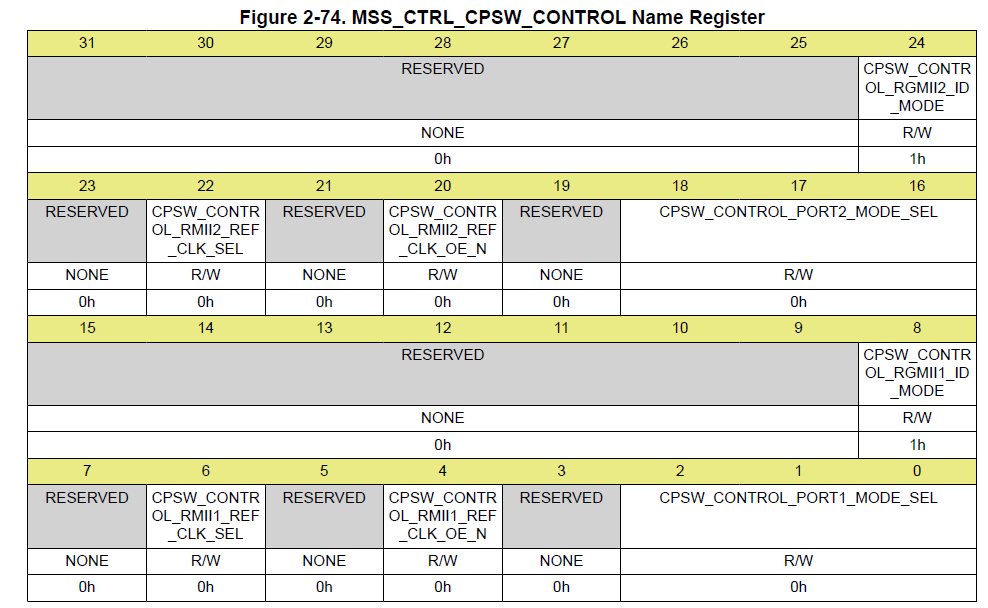

According to TRM, we should be able to generate 50MHz reference clock for RMII1/RMII2.

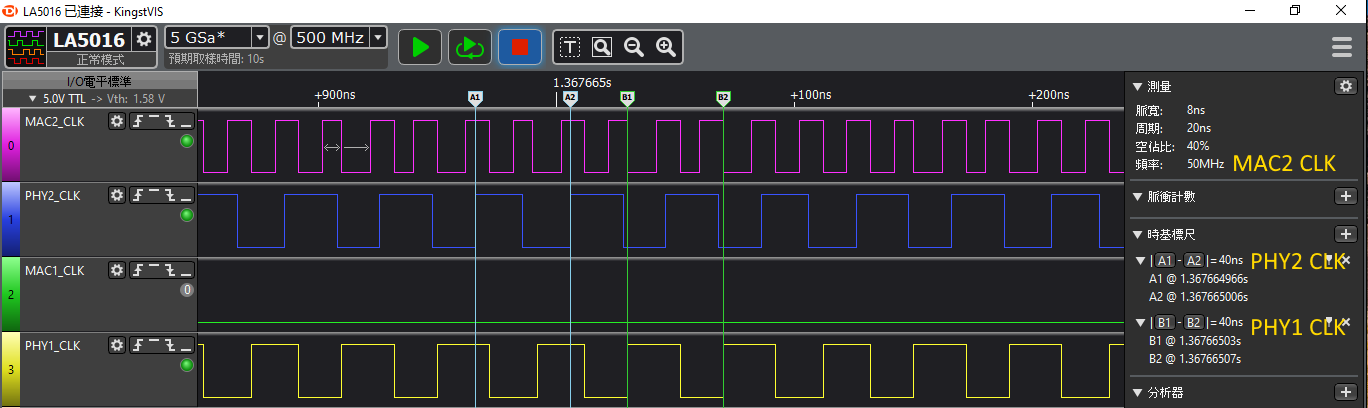

However, when we measure the signal, RMII1_REF_CLK on R17 pin are missing.

We also set R17 as GPIO and toggle it, we can make sure R17 has correct connection. No layout issue.

So we would like to know why we can't generate RMII1_REF_CLK?

Regards

Andre