Other Parts Discussed in Thread: AM263P4

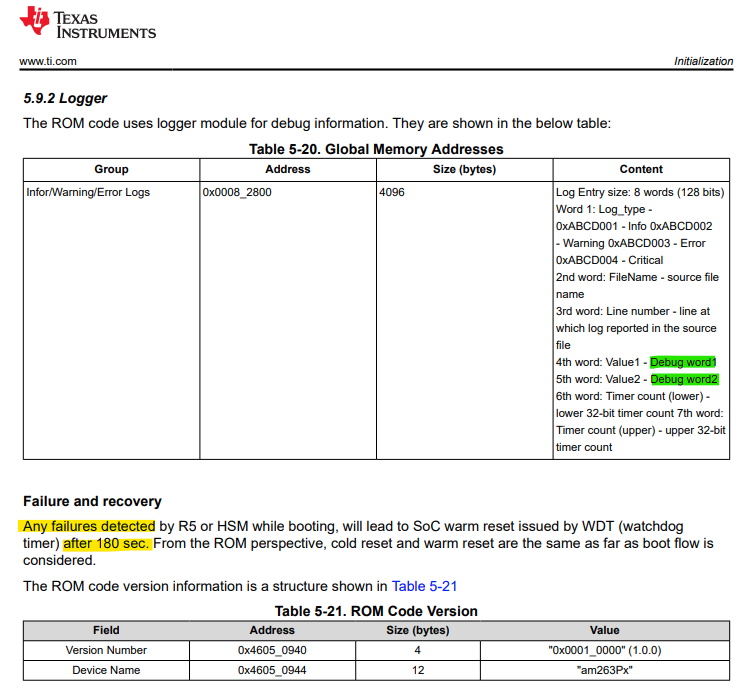

We are currently experiencing an issue where our custom board with the Sitara AM263P4 goes through a reset every 180 seconds when the boot pins are set to DevBoot. On our board the boot pins are switchable through a jumper. The boot pins are currently set to DevBoot and we are debugging a main application. We have found in the technical reference manual a page that states that "Any failures detected... will lead to a warm reset .... after 180 seconds". We have also found the E2E post linked below that states that if none of the boot image locations has a valid image the "system enters panic mode and resets after 180 seconds" but it seems that this is inteded for non DevBoot modes where a boot image is expected.

The questions are:

Why does our system reset after 180 seconds when the boot pins are configured for DevBoot mode?

How do we interpret the "debug words" in section 5.9.2 logger (highligted in green)?

How do we turn off this 180 second reset when in DevBoot for debugging?