Part Number: MSPM0G1507

Other Parts Discussed in Thread: MSPM0G3507

Hi experts,

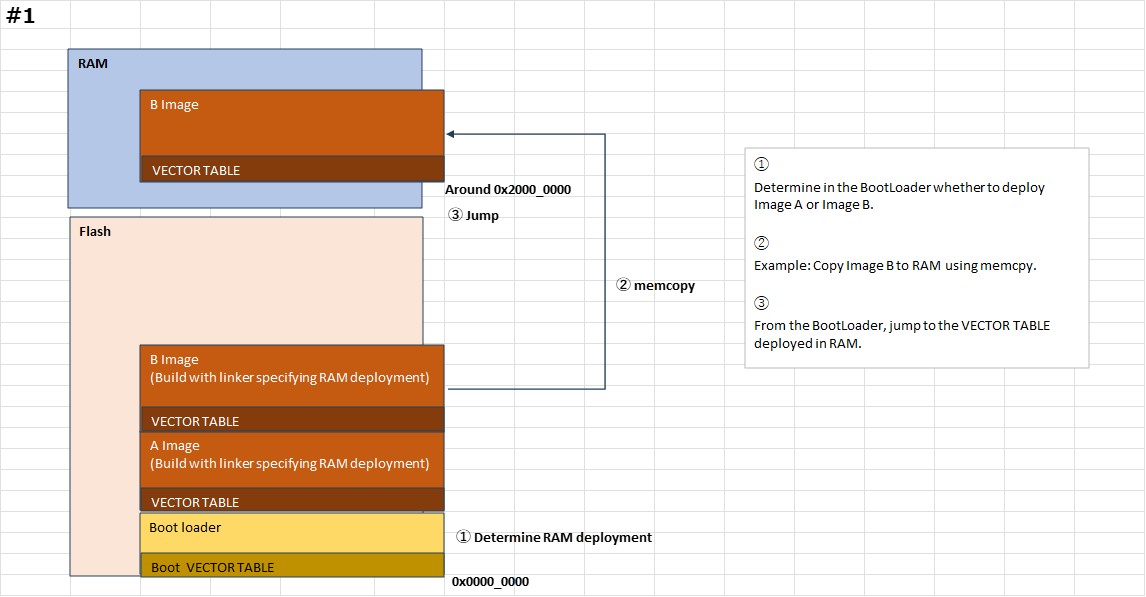

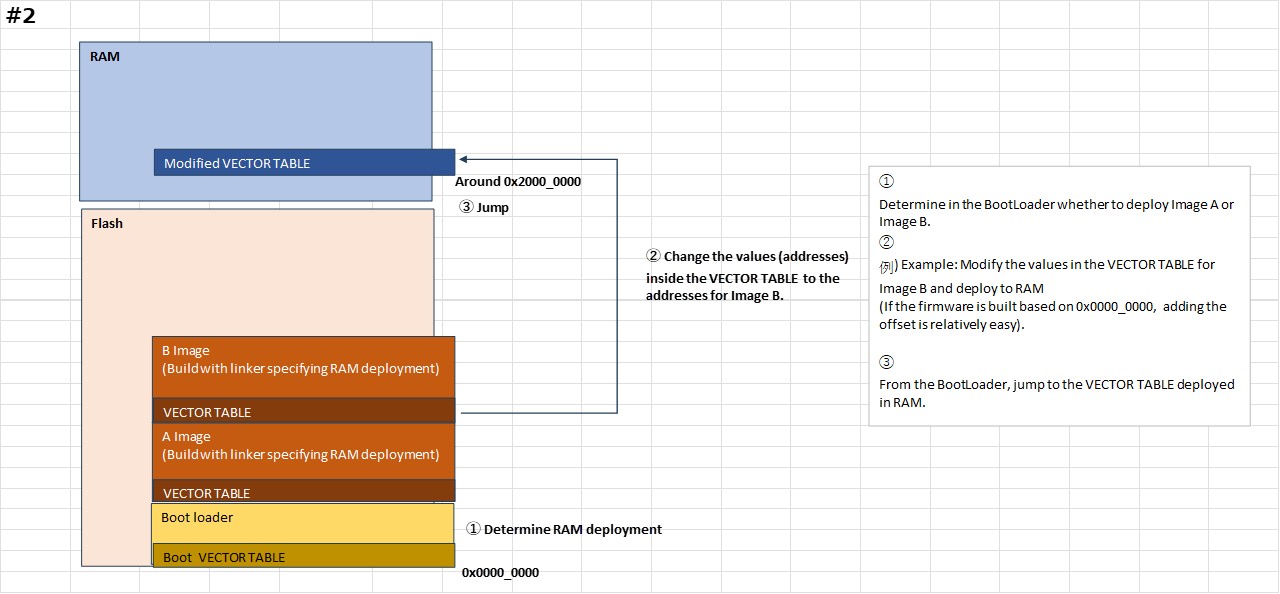

As shown in the diagram below, my customer are considering a configuration where the Flash memory area consists of two images (A and B) and a BootLoader, and the selected image is deployed to RAM for execution.

Q1: Is #1 and #2 feasible?

Q2: If it is feasible, could you please let me know any constraints or concerns?

Q3: Also, could you suggest if there is a better approach?

Additional information / Purpose:

- The goal is to enable firmware (image) switching during operation in the field by deploying to RAM.

- Currently, it is undecided which image (A or B) the user will use, and also undecided which image will be updated during an update process.

- Two sets of table data will be prepared to match the images, and these will also be deployed to RAM.

- Refer: MSPM0G1106: Inquiry About RAM Execution and Release Build on MSPM0G1106 - Arm-based microcontrollers forum - Arm-based microcontrollers - TI E2E support forums

Best regards,

O.H