Part Number: MSPM0L1305

Hi,

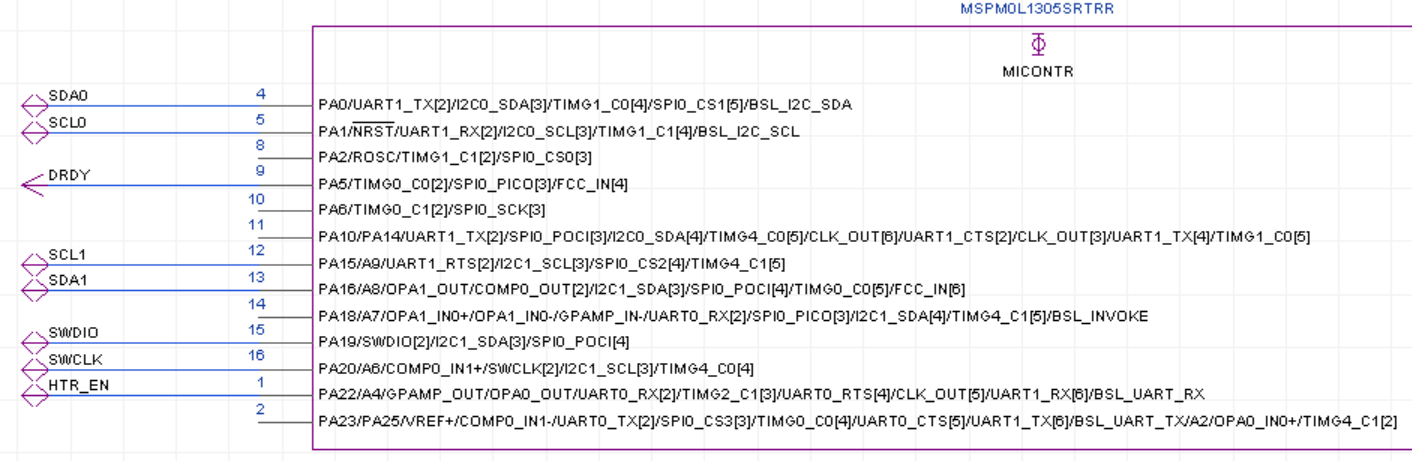

We are using the MSPM0L1305SRTRR in our design, with an estimated annual volume of around 100K units.

I plan to use the internal OPA in buffer mode, with its output routed to the ADC. My understanding is that connecting the input signal to PA18/A7 (pin 14) and configuring this pin as the non-inverting input should be sufficient for the hardware. The rest—such as tying the OPA’s output to its inverting input and routing the OPA output to the ADC—can be handled internally by selecting the appropriate MUX settings. Is this correct? Externally only one pin is enough right?

Additionally, I am using PA0 and PA1 for bootloading via I²C. After bootloading, can these pins be reused as a normal I²C interface supporting Fast-mode Plus (Fm+)?

Please confirm if my understanding is correct or if there are any additional considerations.