Part Number: AM2634

Other Parts Discussed in Thread: AM2632

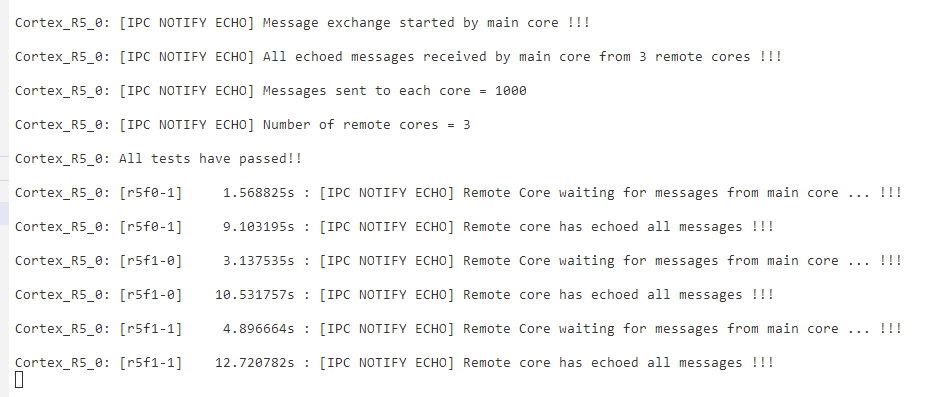

I had successfully debuged the ipc_notify_echo_am263x-lp_system_freertos_nortos demo with luanchpad.

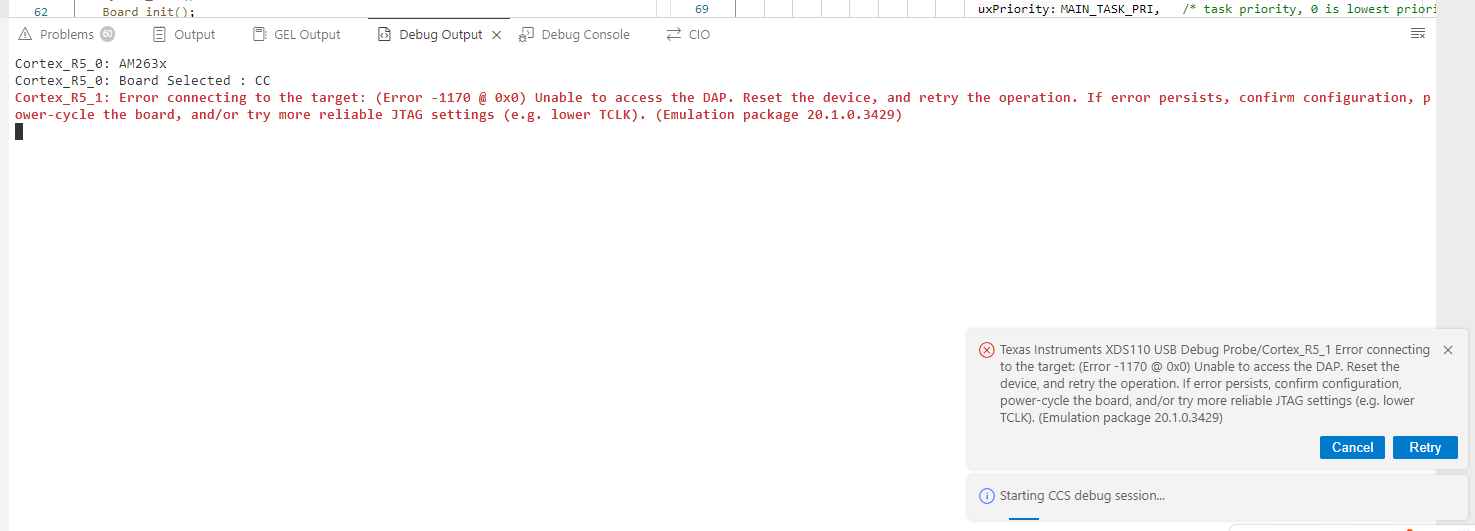

But There is error when I debug this demo with our own board with XDS110. You can see below picture.