Other Parts Discussed in Thread: DRV8363, SYSCONFIG

Hi,

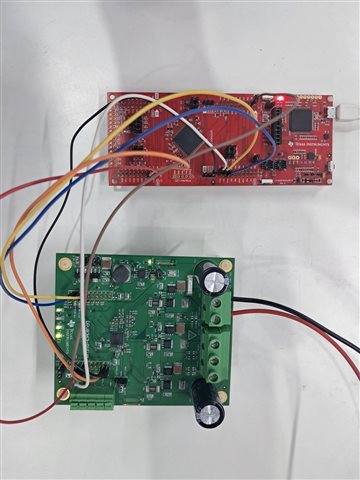

I am working on MSPM0G3519 and DRV8363S.

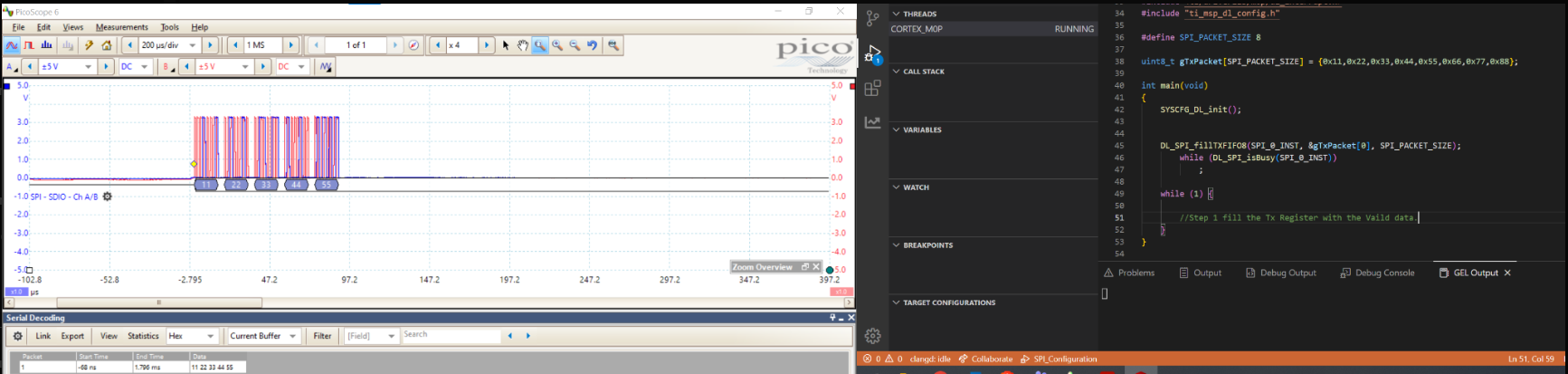

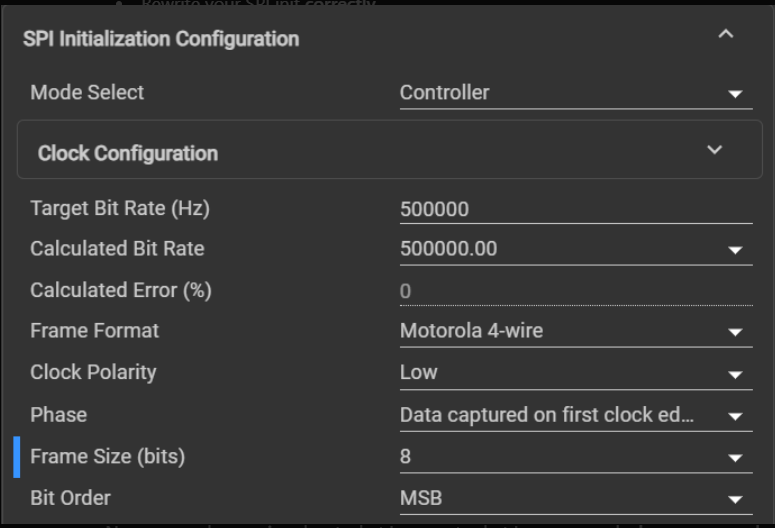

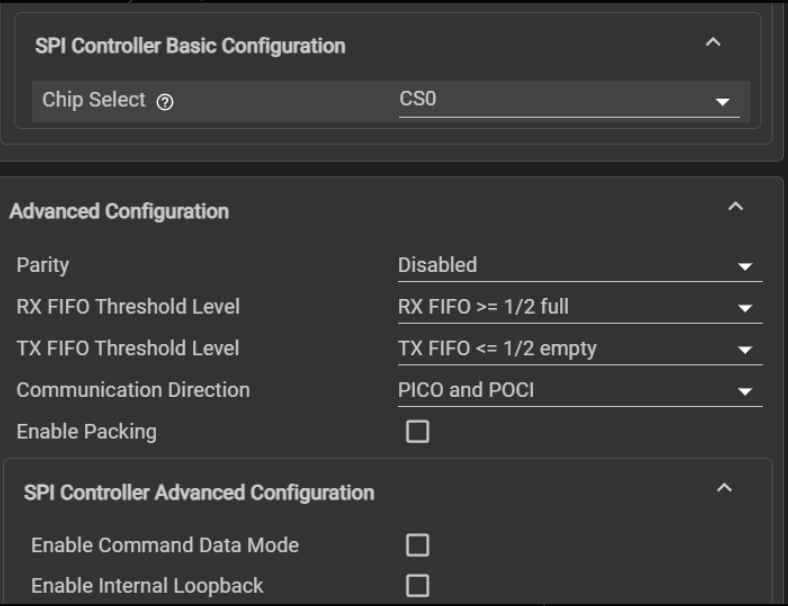

I started with basic SPI peripheral initialization to verify data sent from PICO.

I sent 0x11, 0x22, 0x33, 0x44, 0x55, 0x66, 0x77, 0x88 but only received0x11, 0x22, 0x33, 0x44, 0x55. Also, I have verified that the return value from the function DL_SPI_fillTXFIFO8 is 5.

Why are only 5 bytes transmitted?

Regards,

Sakhan