Part Number: AM263P4

Other Parts Discussed in Thread: SYSCONFIG, ,

Hi,

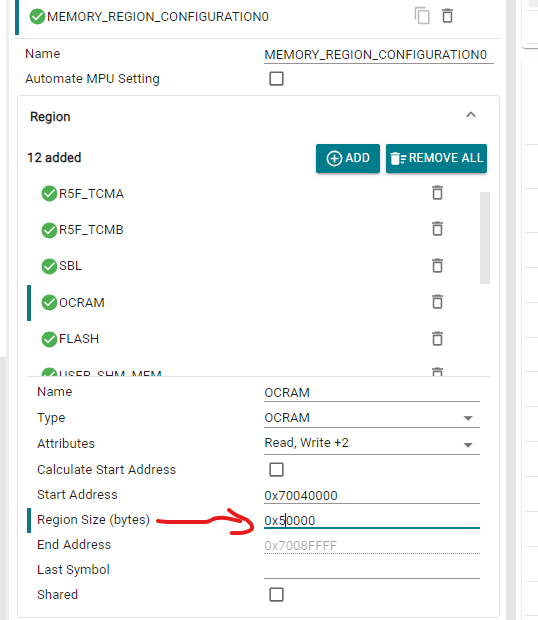

I recently had to enlarge the amount of RAM allocated to my program .text section. So initially I went into sysconfig and increased the pre existing OCRAM memory region from 0x40000 bytes to 0x50000 bytes.

However, this caused a prefetch abort fault during the first register write in OSPI_lld_phyBasicConfig(..) within the Board_flashOpen() call I make at the beginning of my program.

I also realized that the OCRAM banks are seperated out at the following intervals:

L2OCRAM_BANK0 --- start: 0x7000 0000 --- end: 0x7007 FFFF --- size: 512 KB

L2OCRAM_BANK1 --- start: 0x7008 0000 --- end: 0x700F FFFF --- size: 512 KB

L2OCRAM_BANK2 --- start: 0x7010 0000 --- end: 0x7017 FFFF --- size: 512 KB

L2OCRAM_BANK3 --- start: 0x7018 0000 --- end: 0x701F FFFF --- size: 512 KB

...

And thus my current OCRAM memory region which started at 0x70040000 and ended at 0x7008FFFF defined in the sysconfig overlaped between L2OCRAM_BANK0 and L2OCRAM_BANK1.

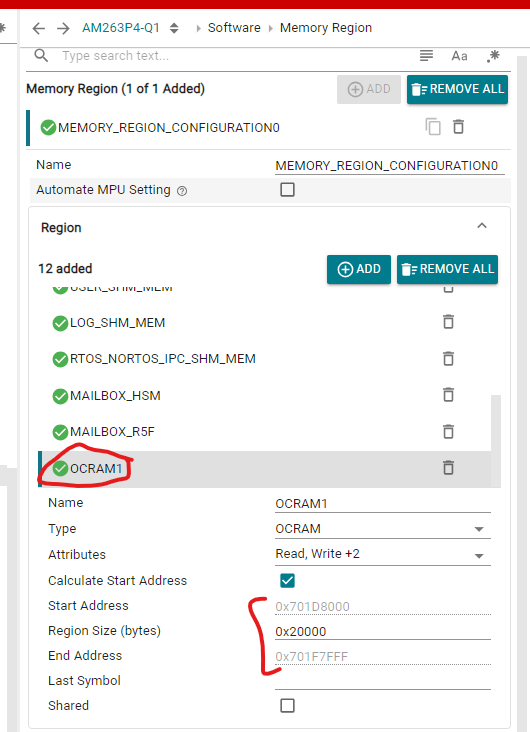

Thinking that this may be an issue I created a new memory region for my linker called OCRAM1 set only inside of L2OCRAM_BANK3. i also set my first OCRAM memory region back to just 0x40000 bytes in size so its only within L2OCRAM_BANK1. I then added OCRAM1 as the memory region used for the section requiring more space.

After making these changes I no longer get the prefetch abort fault and my application runs as expected.

My question is: are memory regions defined for the linker only allowed to be within a single OCRAM bank, i.e. a single memory region can't overlap two OCRAM banks?

Thank you