Part Number: AM2634

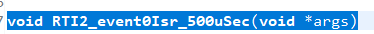

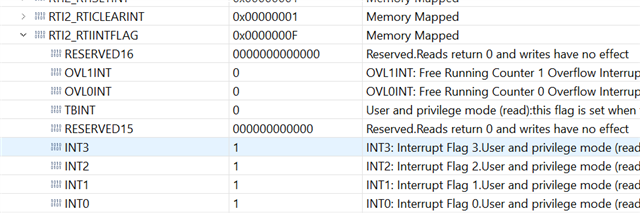

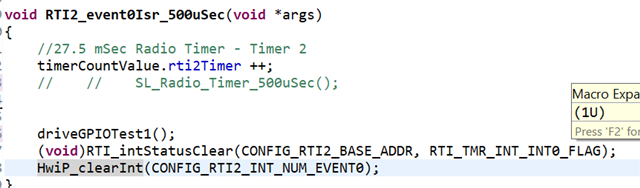

Hi, I need help understanding why my timers stop running while debugging. We are using three different hardware timers in our code (500 µs, 1 ms, and 256 ms). During debugging, one of the timers eventually stops, and its interrupt flag is not getting cleared. We tried changing the stall mode (both ON and OFF), and it is currently set to ON, but the issue persists.

Can someone help me figure out why this is happening? and how to resolve