Part Number: MSPM0L2228

Hi,

During a development of a software for MSPM0L2228, CCS said that "NONMAIN contents corrupted" as you can see a picture below.

Could you tell me the reason of the error, and counter-measures for this issue???

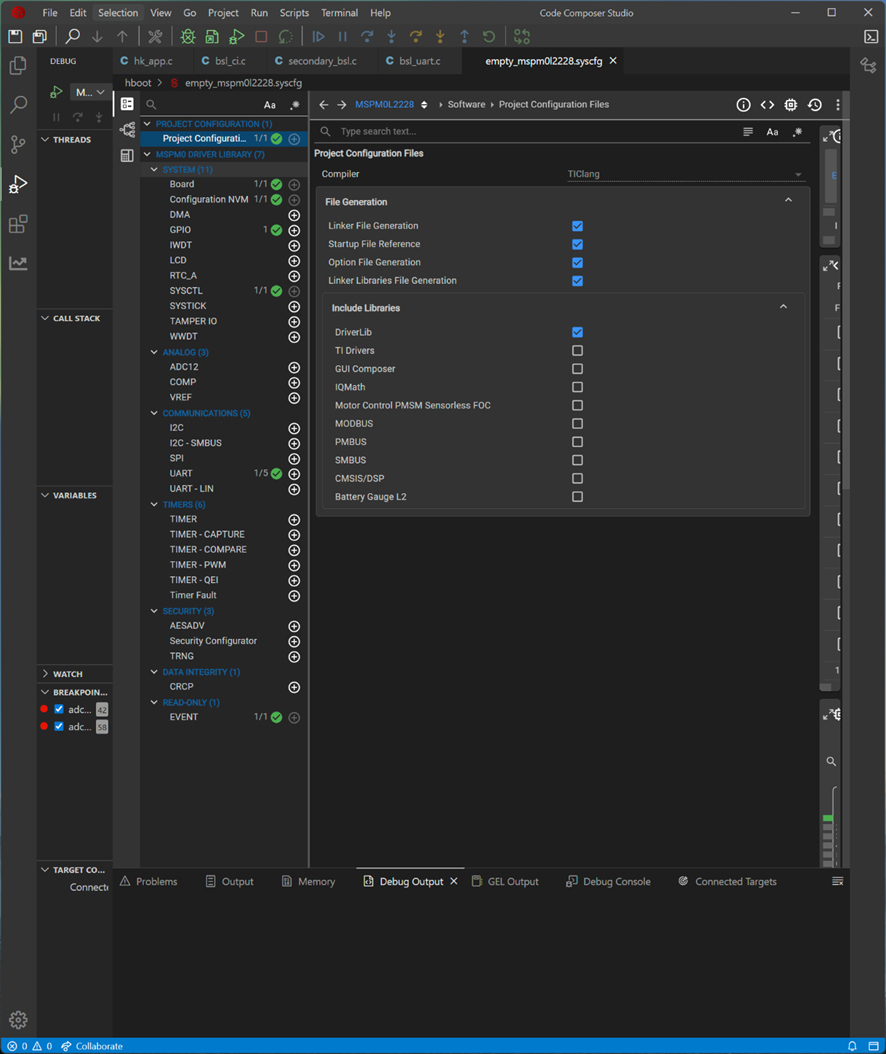

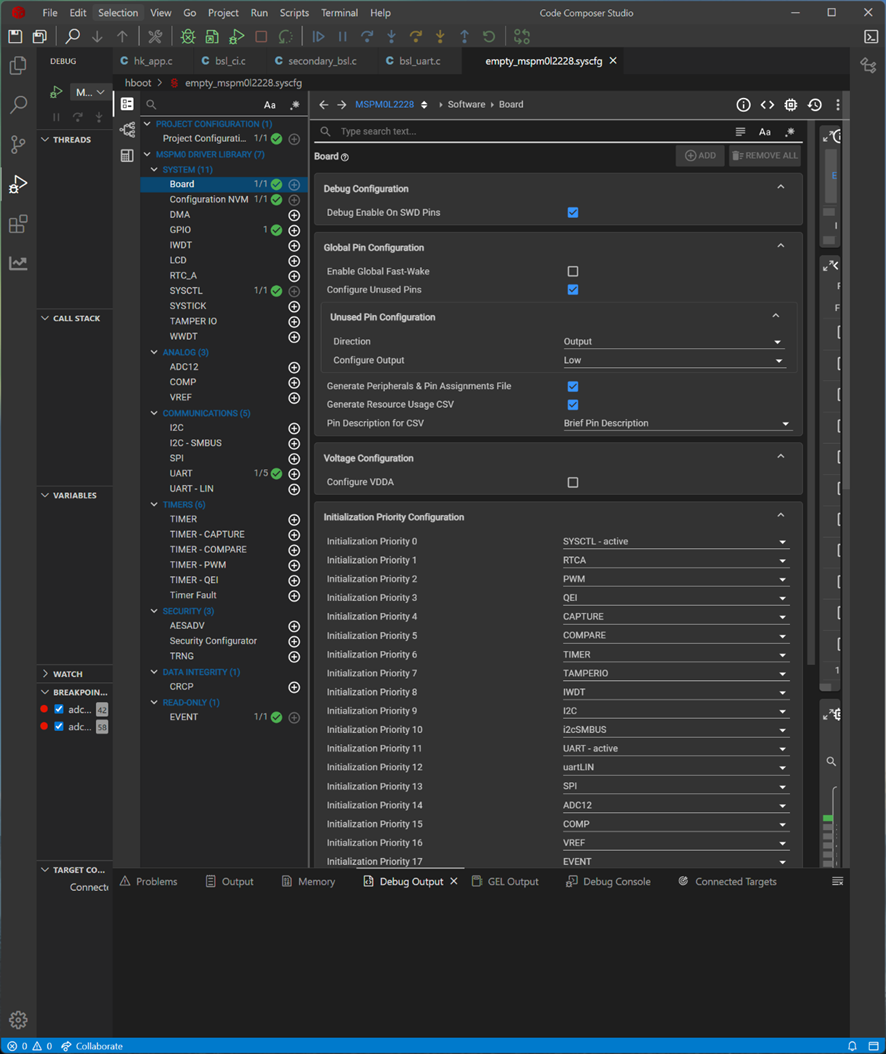

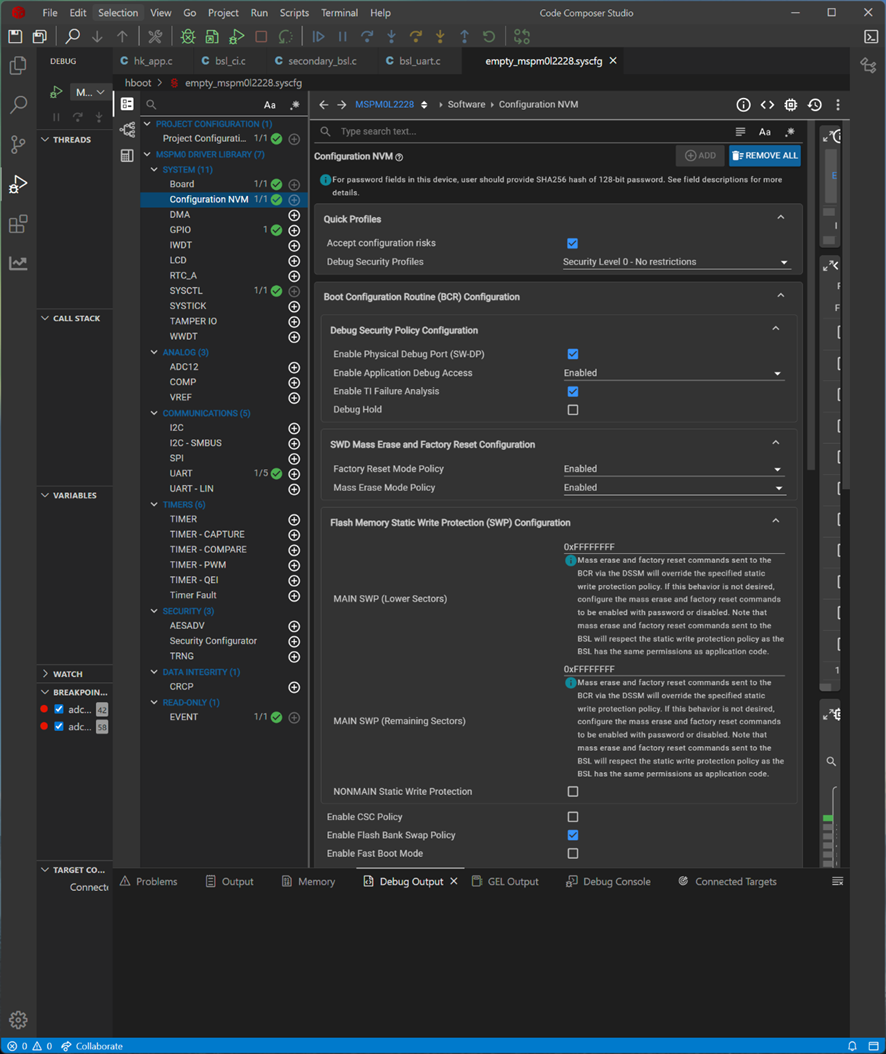

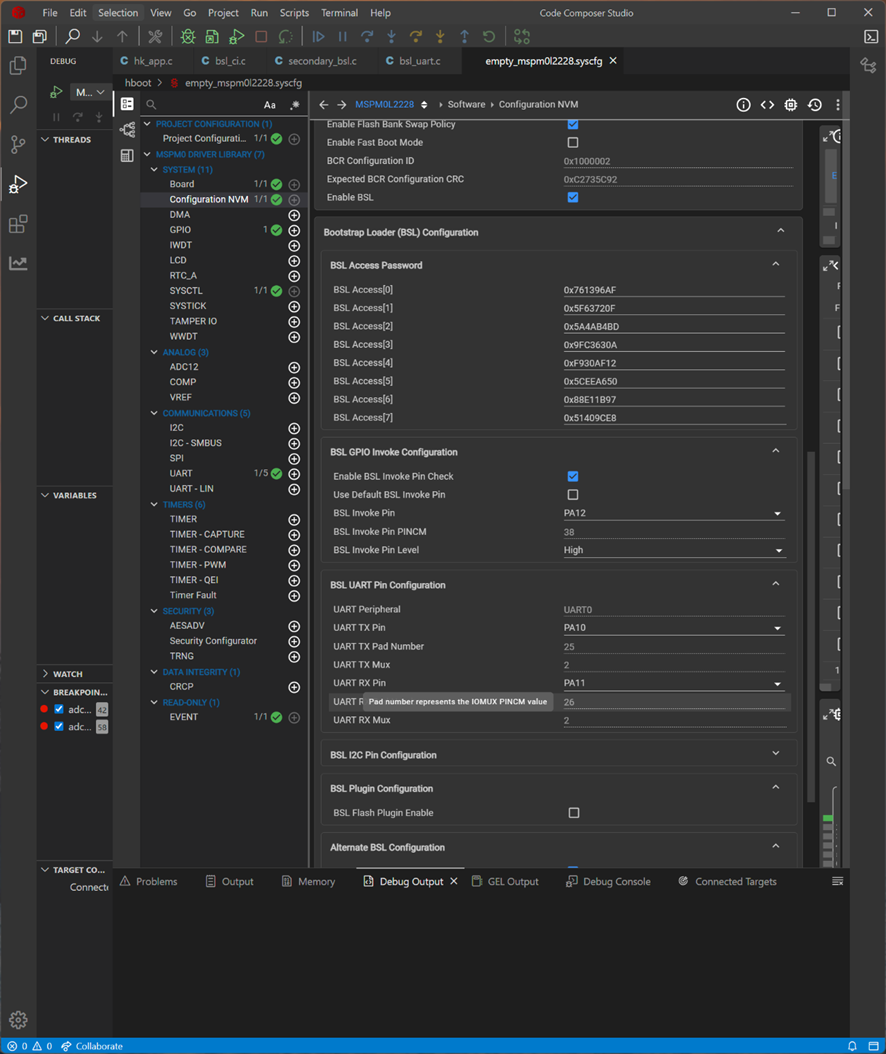

1) Build a software configured as below.

2) Uploaded it to our original PCB w MSPM0.

3) Power OFF and ON.

4) Checked the behaivar of my software.

5) Changed the logic of my software to fit what i wanna do.

6) Uploaded it to our original PCB again.

7) The error message like below apeared on CCS.

Best Regards,

Susumu