Part Number: MSPM0G1518

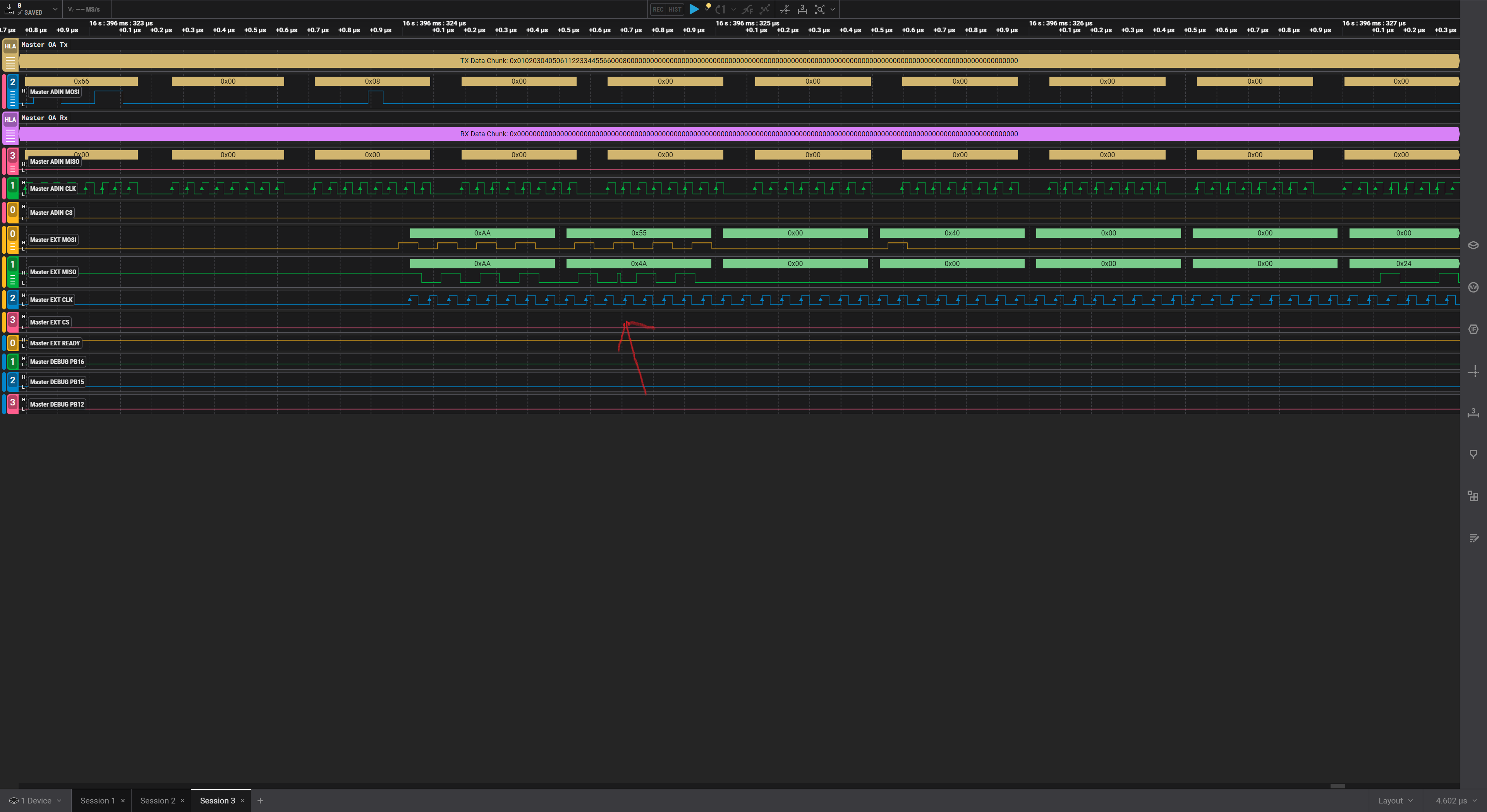

I have a SPI peripheral configured to use two channels of DMA to transmit and receive. I'm consistently seeing a very short SPI transmit bit then the SPI perpheral appears to have bitshifted.

I checked the errata and there's nothing in there that would describe this bug. My first question is why is this happening? The second question is is the only way to recover to reset the SPI peripheral on CS inactive?

I checked the errata and there's nothing in there that would describe this bug. My first question is why is this happening? The second question is is the only way to recover to reset the SPI peripheral on CS inactive?