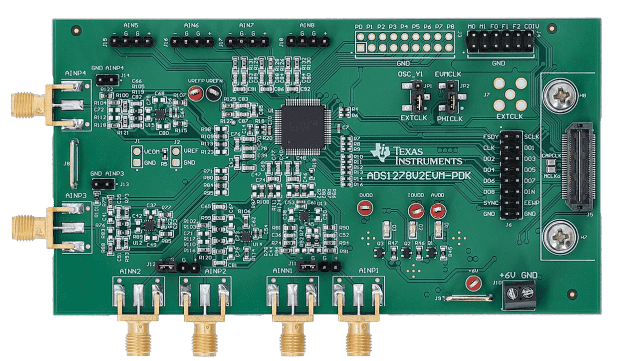

Part Number: ADS1278EVM-PDK

Other Parts Discussed in Thread: ADS1278, ADS127L18

Hello,

I have been looking to interface the ADS1278EVM-PDK from an arm microcontroller using a SPI interface, via the external controller options outlined in the datasheet. I am having some difficulty transferring data (the clock/ drdy pins seem to be functioning, but there seems to be issues reading the data. I have noticed several of the chips available have example drivers/ device tree overlays, are any of these available for this chip/device?

Best Regards,

Joseph Sutlive