We are using TM4C129's SPI with DMA to interface to an SPI slave.

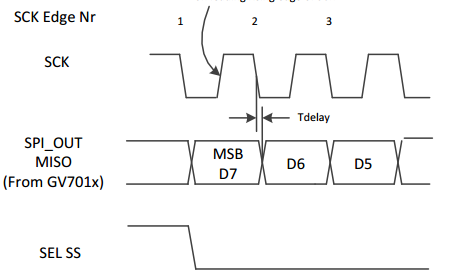

We are using the configuration SPI_POL0_PHA0 (Change data at falling edge, sample data at rising edge)

The problem is that the data sent from slave to TM4C129 is being received correctly... but...

The sent by TM4C129 to slave suffers bit flips in LSB or MSB of some bytes.

We are thinking that the slave might have some requirements on the settling time.

Is there any way we can fine tune the time delay between (introduce delay) CLK and MOSI signals?

Is there any register setting for this?

We want to manually introduce some tdelay as shown in the diagram below