Hi, i'm with a problem in my project with RAM memory.

Then I will explain:

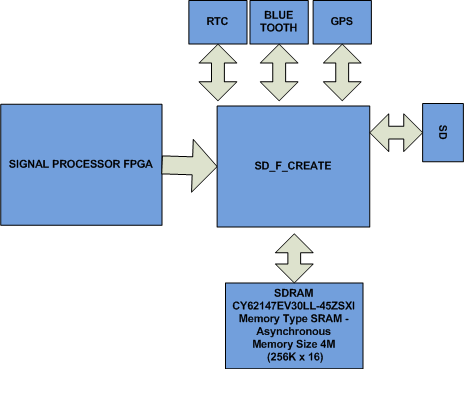

I'm finish a power quality device in my P.h.D, and this device work with 2 processors, one FOGA ( Signal Processing) and ARM (TIVA ) work with manager of system. In my case ARM run GPS/ BLUETOOTH/ RTC (TXCO) AND SDCARD. The communication between FPGA and ARM is executed by SPI bus.

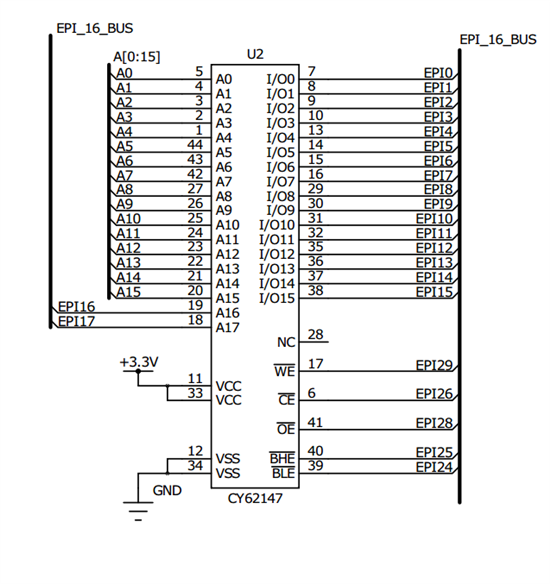

In my prototipe I'm using Stellaris Launchpad, but my problem happen when I need open a new file on SD. During this time ( 2 seconds) I cant buffer(2Mbytes ) that arrive of FPGA. After search about dual port FIFO and other chip to solve this problem, I found TM4C129DNCPDT that can work with external SDRAM/SRAM memory. I would like to receive suggestion about what SDRAM chip that I can put in my board and I will open my files Gerber and software about work this .

Anyone can help me choise a good chip that can work in this situation.