Hello, I have a question about controlling multiple SPI(SSI) slave devices.(Please understand my poor English...)

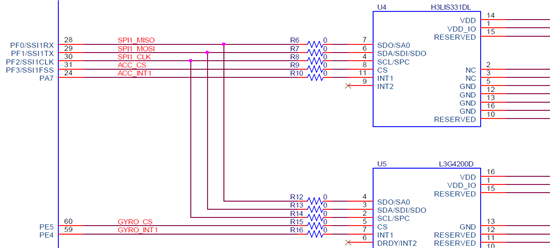

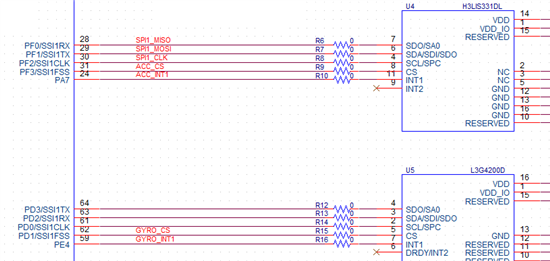

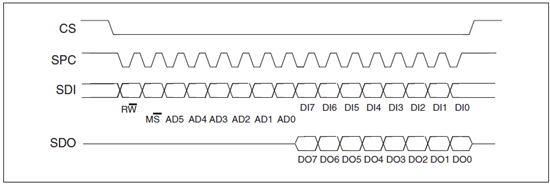

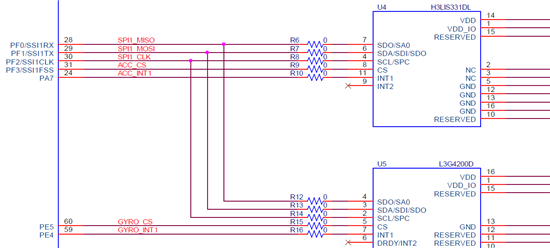

I'm using TM4C123BH6PMI MCU, a 3-axis digital accelerometer(ST H3LIS331DL), and a 3-axis digital output gyroscope sensor(ST L3G4200D).

I'm trying to control these two sensors using SPI interface at SSI1 port.

Which picture is the correct connection?

Are both ways are possible to control both sensors? Or is it not a proper way?

(PE4, PE5 is a GPIO)