Hello,

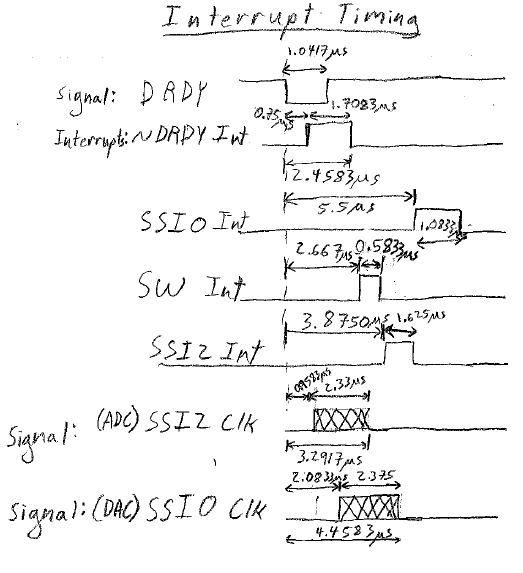

I have the uDMA setup to make a transfer to the SSI0 TX. I also have the SSI0 end of transmission (EOT) interrupt setup to trigger a gpio pulse low. However when I monitor the SSI0 output and the gpio using a logic analyzer I notice that it takes 2 us (CLK =80MHz) from the end of the SSI0 transmission to the start of the pulse that is triggered by the SSI0 EOT interrupt. The Logic analyzer screenshot below shows the problem. (also available in the attached folder) The signals in the screenshot are:

DAC CLK -> SSI 0 CLK

DAC ~SYNC -> SSI0 CS

~LDAC FORCER -> GPIO pulse supposedly generated by SSI0 EOT interrupt

I was really expecting ~LDAC_FORCER to go low immediately following the end of the SSI0 transmission.

I really appreciate any help on this one. I've been working on it for a while now.

My code is attached: 1263.SSI0 - EOT Interrupt Issue - code.zip

Thanks,

Curtis