This discussion has part academic value and part practical value. I believe TI have made an error in their formula for CL, the load capacitance specified by the crystal manufacturer. TI went to great lengths to list specific crystals from a variety of manufacturers for which TI provide calculated values of C1 (=C2 ).

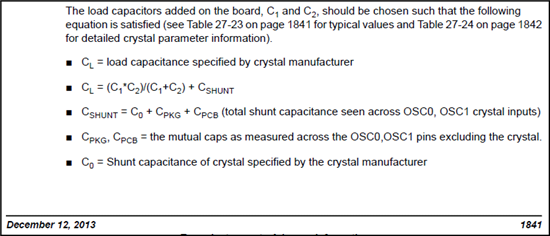

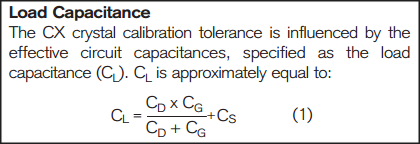

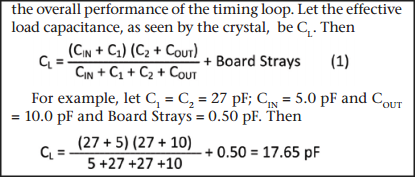

To summarize, I have found NO Crystal manufacturer which requires you to use C0 (the crystal's shunt capacitance) when calculating C1,C2 from CL or visa versa. You can search for yourself for formulas online, and I am happy to copy excerpts from Statek and Abracon in emails they sent me stating this fact. However see below for the formula given by TI as cut from p. 1841 of their datasheet which includes C0.

As long as your chosen crystal's C0 is low enough (e.g. 1-2pF) then in practice the values calculated for C1=C2 are sufficiently similar to those obtained when excluding C0 from the formula. If C0 is higher (e.g. I am using a crystal with C0=7pF) then the values calculated for C1=C2 are nearly half (18pF c.f. 32pF for a given CL of 18pF) ! For some entries in table 27-24, C0=3pF and the resultant values for C1=C2 are too low by about 6pf (i.e. 18pF c.f. 12pF). This could be significant.

Because I want my oscillator to start up first time for the life of my product under all temperature and component tolerances, I wanted to ensure I had a good handle on this aspect of the design so this mistake in TI's formula has lead me to spend a LOT of time trying to make sense of it because I had put implicit trust in TI and initially didn't assume they were wrong. One product recently in development in my company failed to reliably start oscillating and either due to lack of knowledge or misinformation the electrical engineers gave up and opted to drive the OSC pins with an oscillator module instead ! That shows how important it is to ensure the formulas are correct.

Unless your crystal's C0 is >2pF then, you will probably never notice this error nor care about this discussion !