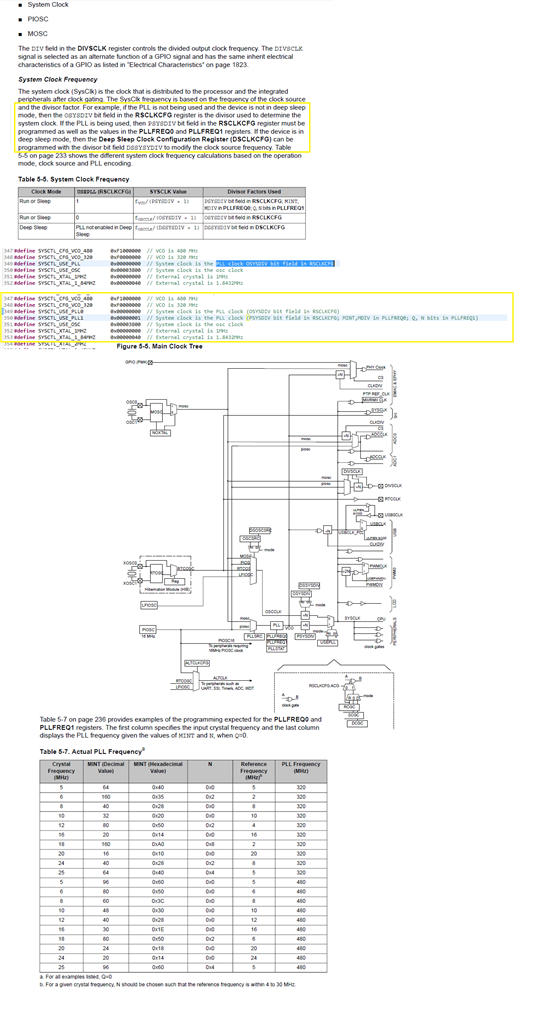

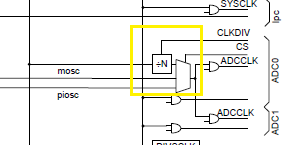

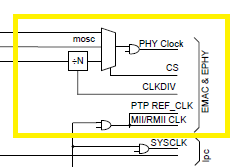

Missing clock configuration as shown in data sheet, Tiva library not keeping consistent with documented clock configuration in a clear and user friendly way. The clock tree implies clock value /N at several peripheral connection nodes yet creating such a configuration appears obscure or not possible in the most recent DL library.

The (Sys_Ctrl_UsePll=0) defined as (Physdiv) must be set (1) in the RSCLKCFG register in order to divide 480 or 320 Mhz PLL VCO for SYSCLK.

Refering to Sysctrl.c function SysCtlClockFreqSet(uint32_t ui32Config, uint32_t ui32SysClock)

Does Sys_Ctrl_UsePll = 0 imply Physdiv or Osysdiv in this function, will adding a #Define (yellow box) work?

Table 5-7 on page 236 provides examples of the programming expected for the PLLFREQ0 and PLLFREQ1 registers. The first column specifies the input crystal frequency and the last column displays the PLL frequency given the values of MINT and N, when Q=0.