The (bl_config.h) holds parameters for the data transport method in transferring the users application object code into the targets flash memory and booting that application from RAM after an MPU reset.

The Boot Loader text states all Tiva processors have a 1024k page length. However the source code listing states "Erasable Page" not writable page and the TM4C1294 erases 2 sectors at a time or a 2Kbyte page.

#Define Flash_Page_Size 0x00000400 = 1024 bytes would then be incorrect when 2Kbyte page 0x000007D0.

Does this source listing below incorrectly use the word (ERASABLE) page or does the function that uses this value need to know the page boundary when erasing before writing new bytes to flash?

// The size of a single, erasable page in the flash. This must be a power of 2. The default value of 1024 bytes represents the page size for the internal flash on all Tiva MCUs and this value should only be overridden if configuring a boot loader to access external flash devices with a page size different from this.

Datasheet:

The interleaved memory prefetchs 256 bits at a time. The prefetch buffers allow the maximum performance of a 120 MHz CPU speed to be maintained with linear code or loops that fit within the prefetch buffer. It is recommended that code be compiled with switches set to eliminate "literals" as much as possible as a literal causes a flash access for that word and a stall for the wait states. Most compilers support transforming literals into "in-line" code, which executes faster in a system where the memory subsystem is slower than the CPU.

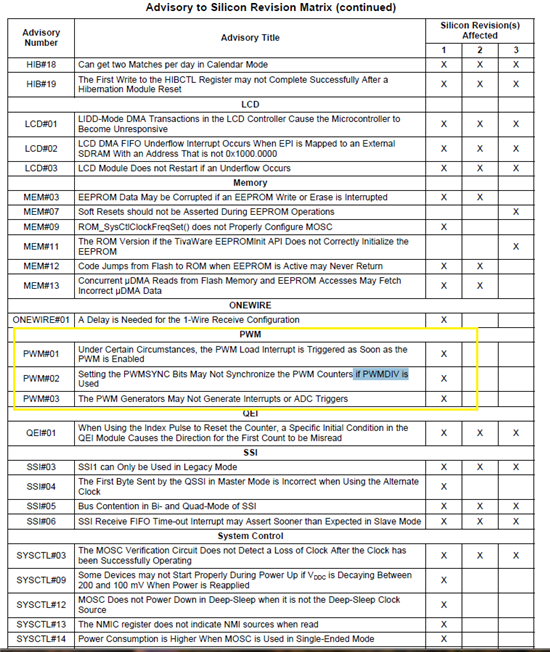

Because the memory is two-way interleaved and each bank individually is an 8-KB sector, when the user erases a sector, using the ERASE bits in the Flash Memory Control (FMC) register, it is a 16 KB erase. Erasing a block causes the entire contents of the block to be reset to all 1s.