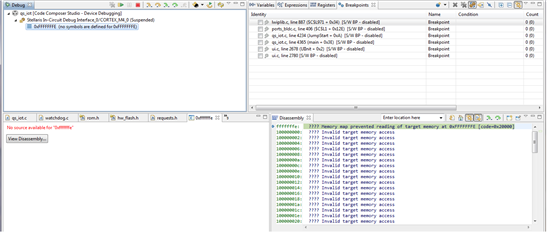

XM4C1294NCPDT after several memory flashes suddenly decides to no longer transfer bytes at the MPU emulator level. As yet have never flashed any SW or unlocked any GPIO port C JTAG 0:3 however pins C7, C4 have been set as analog comparator input pins. The application is flashing the LED's and talking on UART0 to COM3 and a GUI can connect to the target on the Ethernet.

Anyone have some ideas to what might be happening?

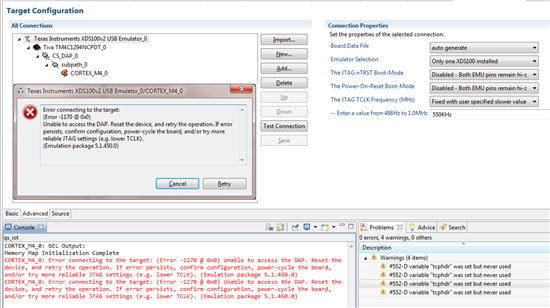

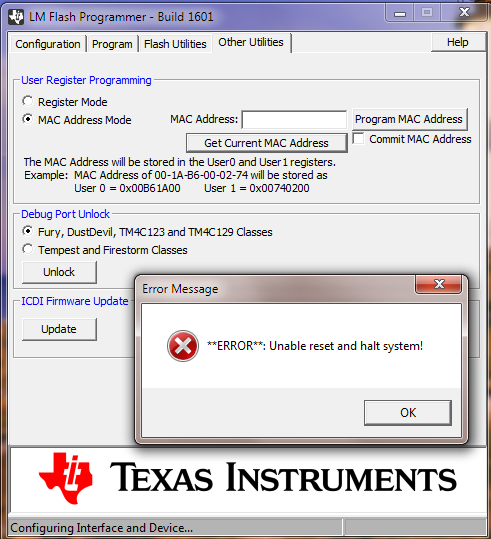

The XDS100V2 passes all loop back tests while the ICDI crashes CCS5.4 upon canceling the failed connection of the DAP though a JTAG connection skips the crash event of (DebugLib.dll). Reinstalled the CCS5.4 Debug server and Stellaris simulator packages did not help. JTAG test

[Start]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\BRETT~1.WIN\AppData\Local\.TI\1655298653\

0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Mar 9 2014'.

The library build time was '22:27:48'.

The library package version is '5.1.450.0'.

The library component version is '35.34.40.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

-----[The log-file for the JTAG TCLK output generated from the PLL]----------

There is no hardware for programming the JTAG TCLK frequency.

-----[Measure the source and frequency of the final JTAG TCLKR input]--------

There is no hardware for measuring the JTAG TCLK frequency.

-----[Perform the standard path-length test on the JTAG IR and DR]-----------

This path-length test uses blocks of 512 32-bit words.

The test for the JTAG IR instruction path-length succeeded.

The JTAG IR instruction path-length is 4 bits.

The test for the JTAG DR bypass path-length succeeded.

The JTAG DR bypass path-length is 1 bits.

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 512 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 512 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End]

Seemingly this behavior occurred after making WatchDog0 and uDMA peripherals present/sleep in the current configuration. The only call to Port C is made in high nibble binary shown below, we can rule that out.

ROM_GPIOPinTypeComparator(GPIO_PORTC_AHB_BASE, GPIO_PIN_7 | GPIO_PIN_4);

Window7 application logs the crash event: Faulting application name: ccstudio.exe, version: 0.0.0.0, time stamp: 0x4d87abff, Faulting module name: DebugLib.dll_unloaded, version: 0.0.0.0, time stamp: 0x50ec252b Exception code: 0xc0000005 Fault offset: 0x68f8a92d, Faulting process id: 0x1550, Faulting application start time: 0x01cf600d2ef99b47,Faulting application path: D:\CCs54\ccsv5\eclipse\ccstudio.exe, Faulting module path: DebugLib.dll, Report Id: 20bae081-cc01-11e3-bca7-00d0b7062877.