I'm using the TM4C123GE6PMI Tiva C part and need some guidance regarding an errata issue for these chips. First what I'm doing:

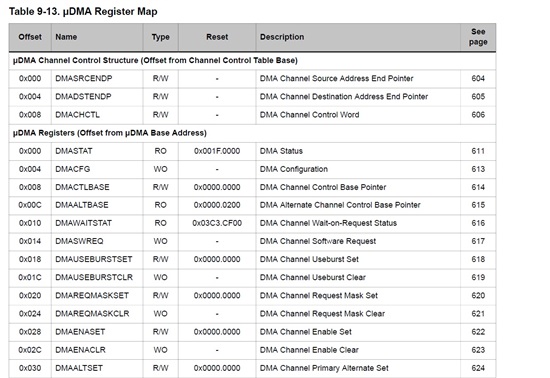

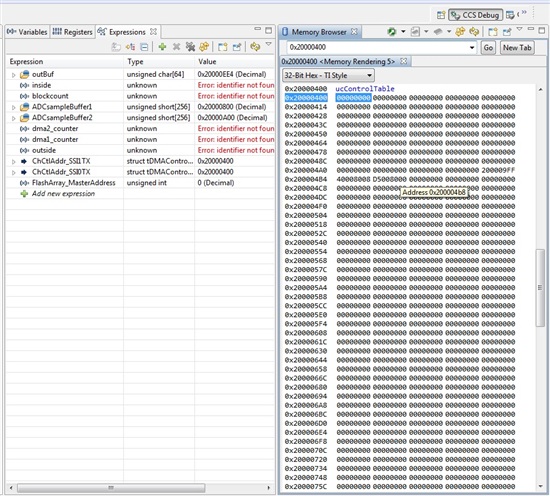

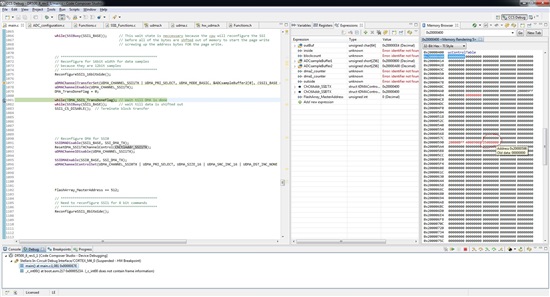

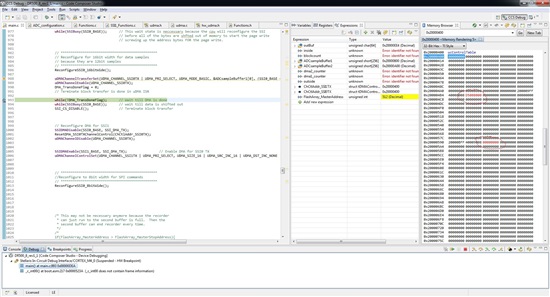

I'm using SSI0 and SSI1 to send data out. I am triggering the DMA to send out blocks of data alternating between the two. I'm unable to use SSI2 or SSI3 in this design. I send out a lot of blocks of data between the two SSI ports so they alternate back and forth thousands of times. After pushing a block out of SSI0 I then push a block out of SSI1 where BOTH SSI's are configured on their seperate DMA channels at all times. I just trigger one channel then the other over and over.

It looks like (so far) that this is working fine. I've gotten the board up and running pushing data out of both as described above and have tested this multiple times where it pushes blocks consisting of 0-256 and when I read the data back out it looks to be all correct.

Potential problem:

In reading the errata for this part I've found that for (per page 17) you can't use peripherals SSI0 and SSI1 on the uDMA. It says "they cannot both be configured to use uDMA". I don't want to move into production if I'm violating the errata, but I'm seeing no issues testing it here on the bench. How do I know if this applies to me? I can't find much info on my revision to know if it is revision 6 and 7? I'm just looking for guidance because I don't want issues to pop up further down the road, but if I don't have to apply the work around (reconfiguring the DMA on the fly) it would save a lot of headache as this chip is pushed pretty hard as is.

Thanks,

Rob