Other Parts Discussed in Thread: TMS570LS1227, TMS570LS2125, TMS570LS20216

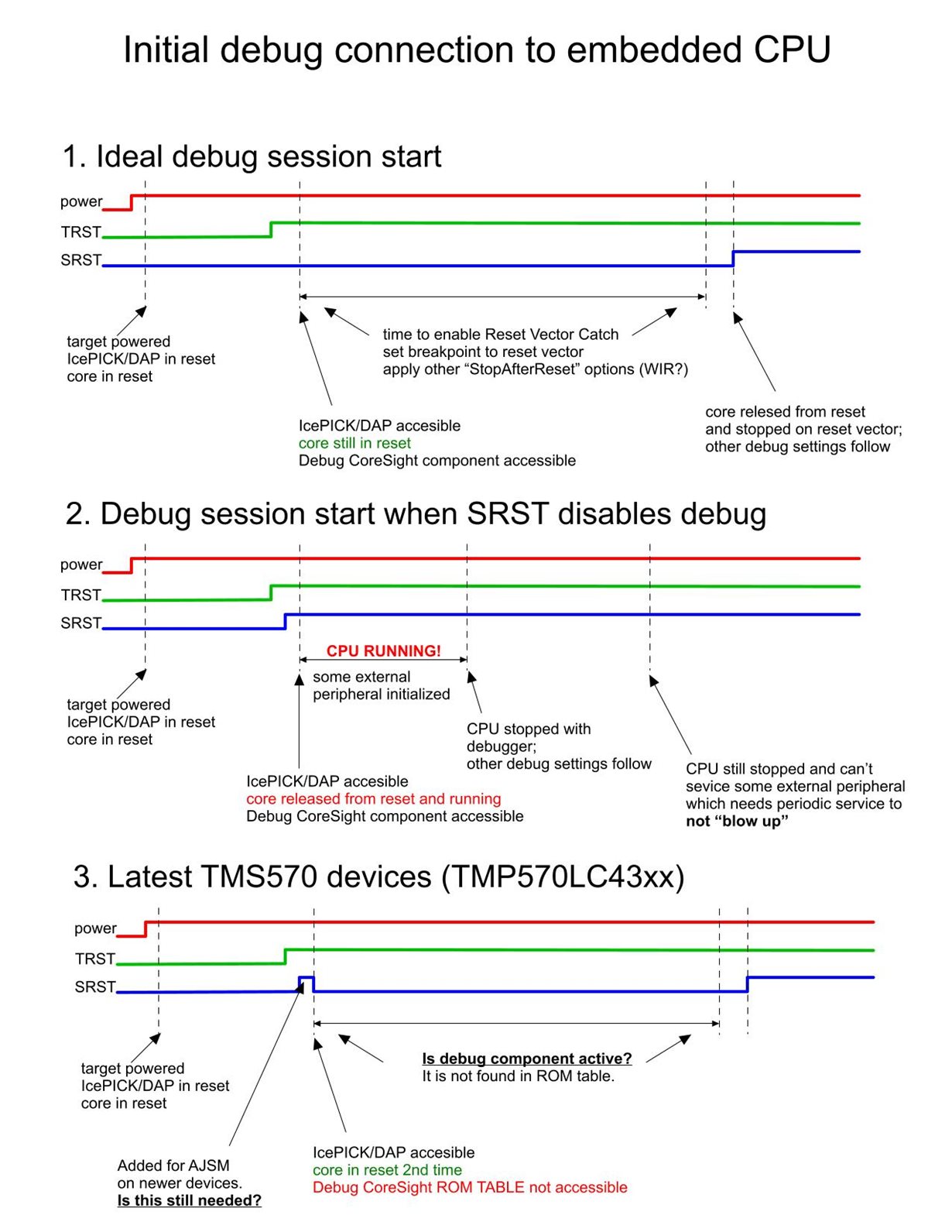

I'm experiencing different debug components behavior on TMS570LC43xx devices from older TMS570 parts. It seems that holding nSRST line low disables access to CoreSight ROM table.

I wish to achieve immediate CPU stop after system reset is released. What is the proper sequence of IcePick and debug registers writes to do this?

I'm attaching an image with further explanation:

I'd like to achieve situation depicted as situation 1.

At the moment I do it like depicted as situation 2.

Situation 3. shows my findings on TMP570LC4357 (notice the P). Can you confirm them?