Hi All,

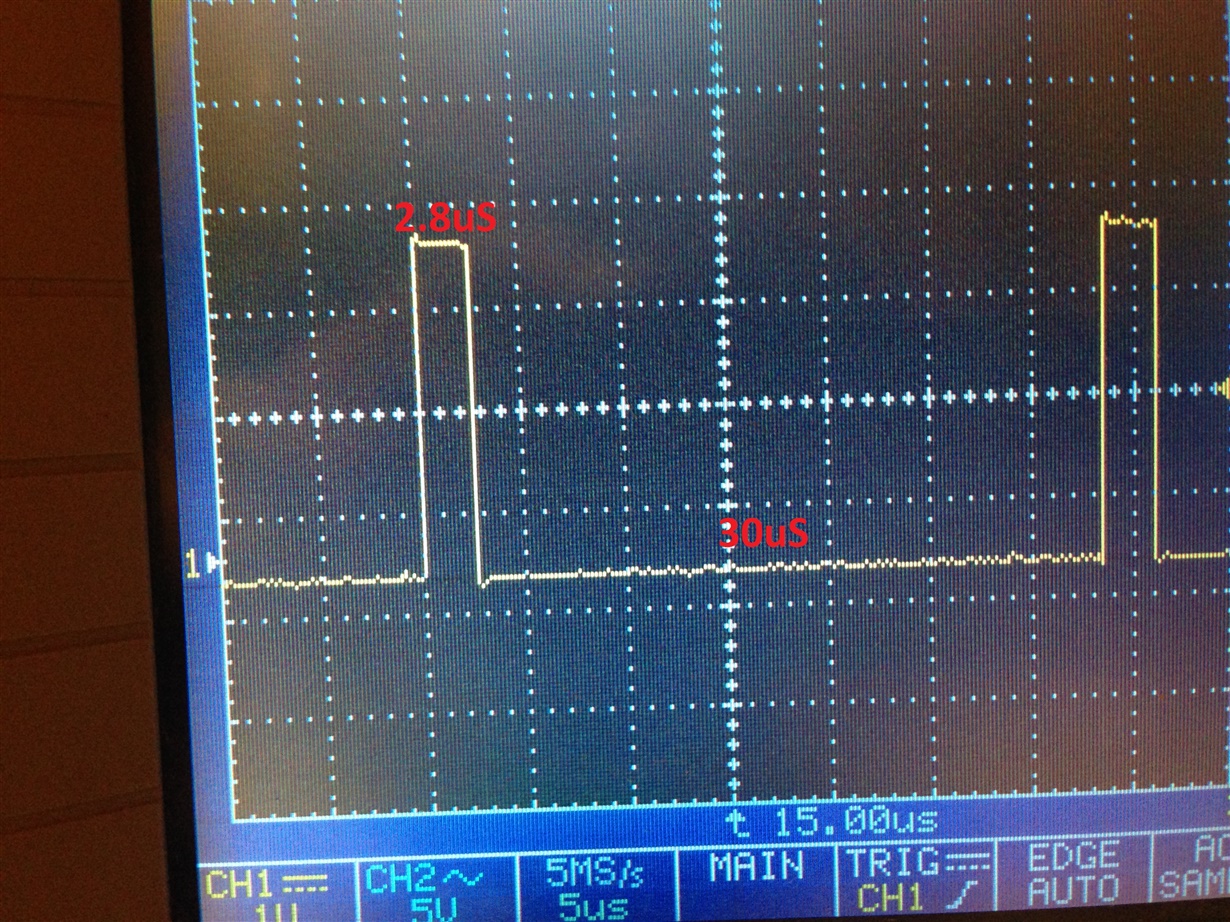

Here is signal which comes to PORT D, Pin 7 of the MCU

Here is code for MCU/GPIO setup:

main(void)

ROM_FPULazyStackingEnable();

ROM_FPULazyStackingEnable();

//on-board OSC 25MHz, MCU - 80MHz

ROM_SysCtlClockSet(SYSCTL_SYSDIV_2_5 | SYSCTL_USE_PLL | SYSCTL_XTAL_25MHZ | SYSCTL_OSC_MAIN);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);// Enable port D

ROM_GPIOPinTypeGPIOInput(GPIO_PORTD_BASE, GPIO_PIN_7);

GPIOPadConfigSet ( GPIO_PORTD_BASE,// Enable weak pullup resistor for PD7

GPIO_PIN_7,

GPIO_STRENGTH_2MA,

GPIO_PIN_TYPE_STD_WPU);

GPIOIntDisable (GPIO_PORTD_BASE, // Disable interrupt

GPIO_PIN_7);

GPIOIntClear (GPIO_PORTD_BASE, // Clear pending interrupts

GPIO_PIN_7);

GPIOIntRegister (GPIO_PORTD_BASE, // Register our handler function for port of D channel

IntDRDY);

GPIOIntTypeSet (GPIO_PORTD_BASE, // Configure for falling edge trigger

GPIO_PIN_7,

GPIO_BOTH_EDGES);//GPIO_LOW_LEVEL);//GPIO_BOTH_EDGES);

GPIOIntEnable (GPIO_PORTD_BASE, // Enable interrupt for the port

GPIO_PIN_7);

while(1){};

}

and here is interrupt handler

void

IntDRDY(void){

uint32_t ui32Value;

ui32Value = GPIOIntStatus(GPIO_PORTD_BASE, true);

if (GPIOIntStatus(GPIO_PORTD_BASE, false) & GPIO_PIN_7) { //check

//GREEN LED on

ROM_GPIOPinWrite(GPIO_PORTA_BASE, GPIO_PIN_2, GPIO_PIN_2);

GPIOIntClear(GPIO_PORTD_BASE, GPIO_PIN_7); // Clear interrupt flag (!)

// if not clear interrupt call continuosly

}

}

the interrupt handler executes only when GPIO_LOW_LEVEL is set, GPIO_FALLING_EDGE/GPIO_RISING_EDGE/GPIO_BOTH_EDGES/GPIO_HIGH_LEVEL do not work.

What could be wrong?

Thanks for any advice!