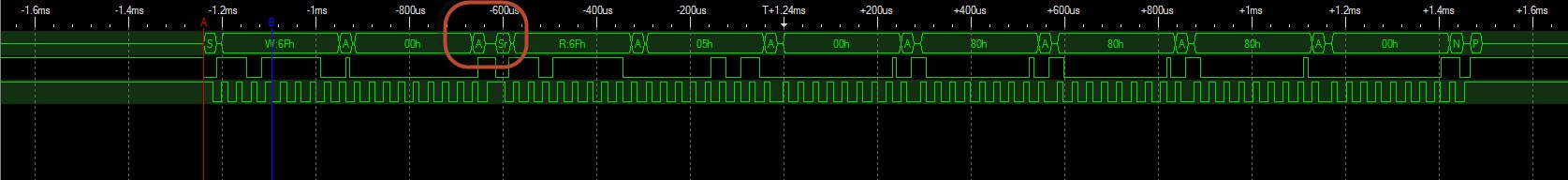

The Tiva "Utils" directory includes what appears to be a very nice SMBus interface that sits on top of I2C.

I don't understand where to hook in SMBusMasterIntProcess. The documentation says it is called from the ISR - but which interrupt? A little example would be great.