Hello everyone, I am currently developing a DC motor current controller based on the TM4C123GLX launchpad board.

I'm trying to measure the current of DC motor trough an ADC channel. The idea is to trigger ADC captures trough the PWM of the motor, each time the current crosses it's mean value. This event occurs right in the middle of the high and low semi-cycles of the PWM, therefore, I would like to trigger a capture on each semi-cycle.

example:

Period: 10 ms

duty cycle: 30%

=> ADC capture 1 at 1,5 ms after the rising edge

=> ADC capture 2 at 3.5 ms after the falling edge

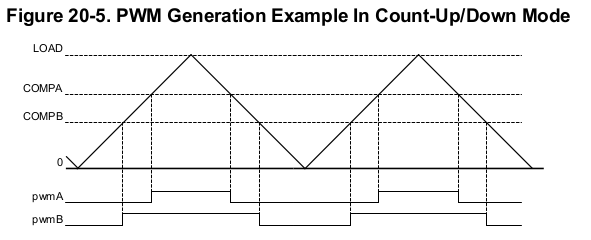

I've been looking throughout the TivaWareC documentation in order to understand how does the PWM module behaves when I feed PWMGenIntTrigEnable() with one of the following trigger parameters PWM_TR_CNT_AU, PWM_TR_CNT_AD, PWM_TR_CNT_BU, PWM_TR_CNT_BD, but i couldent figure out what do they exactly do.

My question are:

- What do the previously stated configurations do?

- Should I change the load of the PWM every time I modify its duty cycle in order to trigger ADC captures at the right time with the PWM_TR_CNT_LOAD configuration? or is there a cleaner way to achieve my goal, in which a capture is performed on every semi-cycles no matter the duty cycles' value.

Thanks in advance,

Claus