hi ti,

in tms570ls0432 datasheet it s mentioned as 8-bti baud clock generator

in TRM it is mentione as 11- bit baud clock generator. which is correct????

it is also specified that the maximum baud rate is 20MHz.

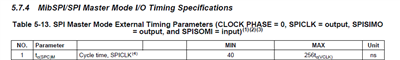

in timing specifications , SPICLK minimum cycle time is 40ns. hence frequency is 25MHz....

why it s limited to 20MHz.....???

then in registers, if prescale is 0 then SPICLK = VCLK/2 = 40MHz...

which should be used????