Hello,

I am trying to use MIBSPI3 as a master to TX and RX. I can currently get it to transfer, but I am not sure how to get the data from MIBSPI RX RAM to DMA to system RAM. I can get the data and see it in the RX RAM using loopback. How to I get the DMA on the RX RAM to trigger? Is it by chaining?

I have been playing with the demo code and looking through the forum, but I haven't been able to make any progress.

Thank you,

Alex

mibspiEnableLoopback(mibspiREG3, Analog_Lbk);

dmaReqAssign(0,15);

g_dmaCTRLPKT.SADD = (uint32)&txData; /* source address */

g_dmaCTRLPKT.DADD = (uint32)(&(mibspiRAM3->tx[0].data)); /* destination address */

g_dmaCTRLPKT.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT.FRCNT = 1; /* frame count */

g_dmaCTRLPKT.ELCNT = dsize; /* element count */

g_dmaCTRLPKT.ELDOFFSET = 4; /* element destination offset */

g_dmaCTRLPKT.ELSOFFSET = 0; /* element source offset */

g_dmaCTRLPKT.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT.FRSOFFSET = 0; /* frame source offset */

g_dmaCTRLPKT.PORTASGN = 4; /* port b */

g_dmaCTRLPKT.RDSIZE = ACCESS_8_BIT; /* read size */

g_dmaCTRLPKT.WRSIZE = ACCESS_8_BIT; /* write size */

g_dmaCTRLPKT.TTYPE = FRAME_TRANSFER ; /* transfer type */

g_dmaCTRLPKT.ADDMODERD = ADDR_INC1; /* address mode read */

g_dmaCTRLPKT.ADDMODEWR = ADDR_OFFSET; /* address mode write */

g_dmaCTRLPKT.AUTOINIT = AUTOINIT_ON; /* autoinit */

/* - setting dma control packets */

dmaSetCtrlPacket(DMA_CH0,g_dmaCTRLPKT);

/* - setting the dma channel to trigger on h/w request */

dmaSetChEnable(DMA_CH0, DMA_SW);

dmaReqAssign(1,14);

g_dmaCTRLPKT.SADD = (uint32)(&(mibspiRAM3->rx[0].data)); /* source address */

g_dmaCTRLPKT.DADD = (uint32)&rxData; /* destination address */

g_dmaCTRLPKT.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT.FRCNT = 1; /* frame count */

g_dmaCTRLPKT.ELCNT = dsize; /* element count */

g_dmaCTRLPKT.ELDOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT.ELSOFFSET = 4; /* element source offset */

g_dmaCTRLPKT.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT.FRSOFFSET = 0; /* frame source offset */

g_dmaCTRLPKT.PORTASGN = 4; /* port b */

g_dmaCTRLPKT.RDSIZE = ACCESS_8_BIT; /* read size */

g_dmaCTRLPKT.WRSIZE = ACCESS_8_BIT; /* write size */

g_dmaCTRLPKT.TTYPE = FRAME_TRANSFER ; /* transfer type */

g_dmaCTRLPKT.ADDMODERD = ADDR_OFFSET; /* address mode read */

g_dmaCTRLPKT.ADDMODEWR = ADDR_INC1; /* address mode write */

g_dmaCTRLPKT.AUTOINIT = AUTOINIT_ON; /* autoinit */

/* - setting dma control packets */

dmaSetCtrlPacket(DMA_CH1,g_dmaCTRLPKT);

/* - setting the dma channel to trigger on h/w request */

dmaSetChEnable(DMA_CH1, DMA_SW);

/* - configuring the mibspi dma , channel 0 , tx line -0 , rxline -1 */

/* - refer to the device data sheet dma request source for mibspi tx/rx */

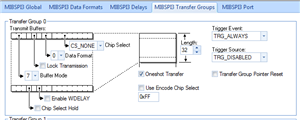

mibspiDmaConfig(mibspiREG3,0,14,15);

dmaEnableInterrupt(0, FTC);

/* - enabling dma module */

dmaEnable();

/* - start the mibspi transfer tg 0 */

mibspiTransfer(mibspiREG3,0 );

/* ... wait until transfer complete */

while(!(mibspiIsTransferComplete(mibspiREG3,0)))

{

};

/* copy from mibspi ram to sys ram */

//----------------------------SD

while(1); /* loop forever */