Other Parts Discussed in Thread: TM4C1231H6PM

Hello,

I’d like to share a knowledge related to a problem with SSI0 port of TIVA TM4C1231H6PM silicon revision 6.

SSI0 port (pins PA2 to PA5) works in SPI slave configuration.

Problem:

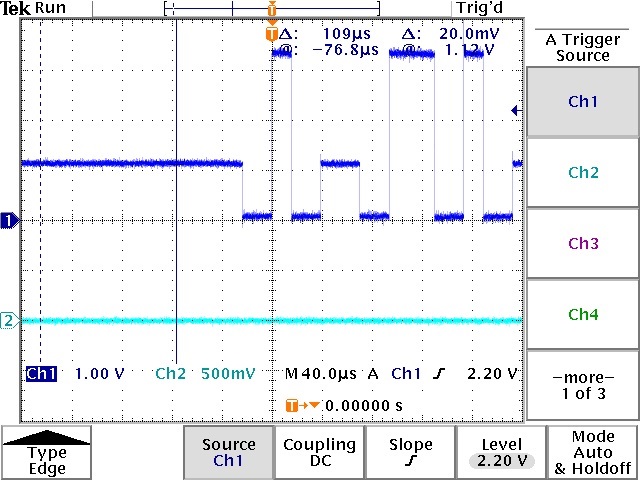

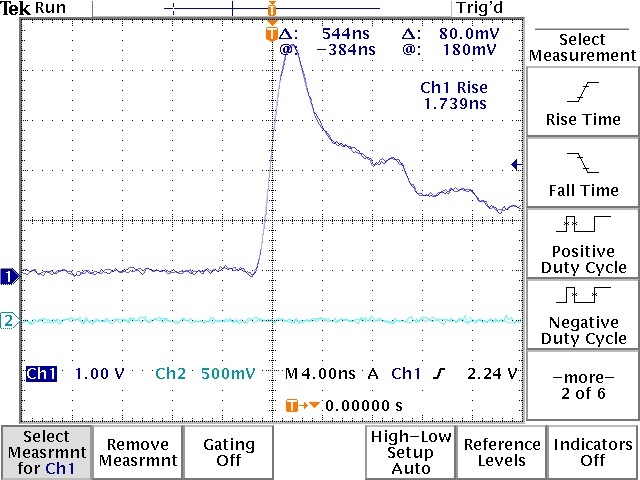

For Tiva’s case temperature above 80 C degrees, the SPI communication is lost (Tiva clips the voltage on SPI inputs pins (SSI0FS, SSI0CK, SSI0RX) to a value 1V). All signals below were measured with 8pF, 10:1 oscilloscope probe.

=========== The figures below shows SSI0RX signal. ===========

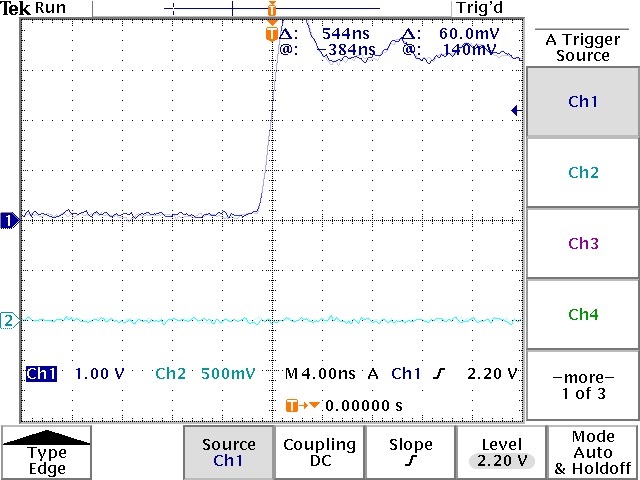

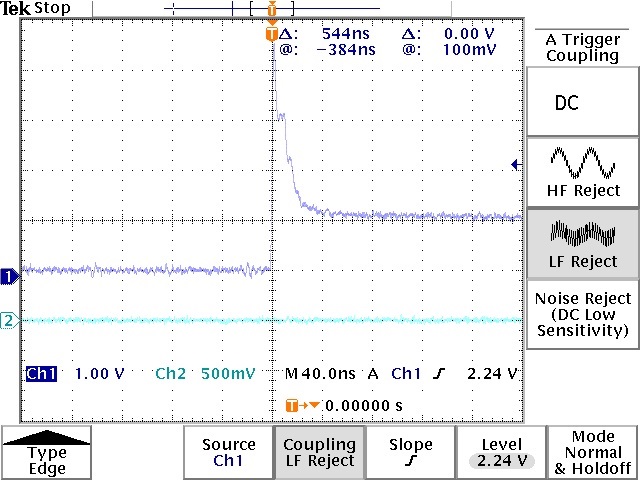

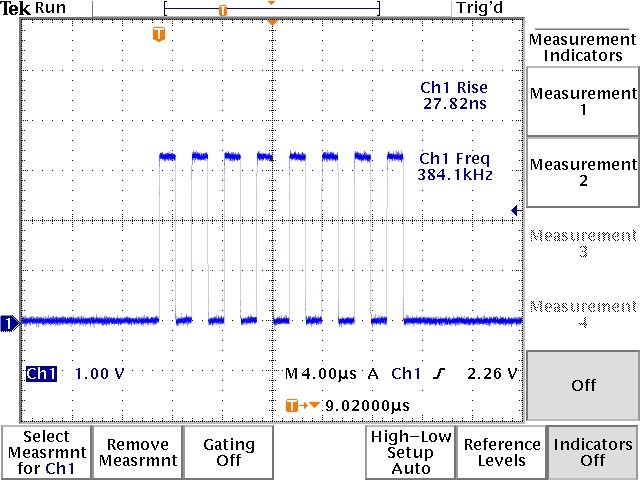

===========Figures below show SSI0CK input: ===========

More details about environment:

Tiva is on one PCB, DSP processor the Tiva communicates with is on another PCB. Both PCBs are connected by means of short pinheader.

Tiva SSI0 pins SSI0CK, SSI0FS, SSI0RX are directly connected to DSP (paths length up to 12 cm)

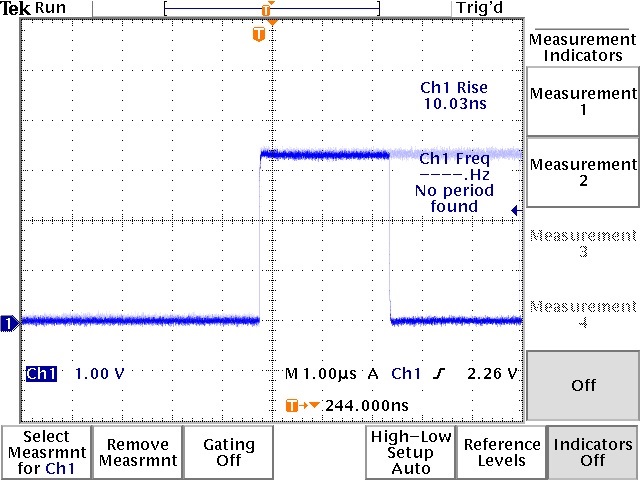

Tiva SSI0 pin SSI0TX is connected to DSP by 100 ohms serial resistor (paths length up to 12 cm, resistor placed near to DSP).

SPI clock frequency equal to 384 kHz.

CPU Clock set to 25MHz (from 8MHz crystal).

The problem was observed when whole device works in ambient tempearature equal to 70 C degrees. In these conditions, the temperature on the Tiva (thermocouple directly attached to top side of Tiva’s case) was about 82-85 C degrees.

For investigation purposes we open the device and heat directly the Tiva from the bootom side (on opposite side of PCB). Thermocouple was attached to top side of Tive case.

The problem appears for termocouple temperature in range 80-85 C degrees.

The problem disappears for termocouple temperature in range 77-80 C degrees.

3-5 C degrees histeresis was observed.

Communication error was asserted repeatidly with every temperature change.

Problem resolution:

Looking for the problem solution we have found problem GPIO#10 in silicon errata: http://www.ti.com/lit/er/spmz849d/spmz849d.pdf .

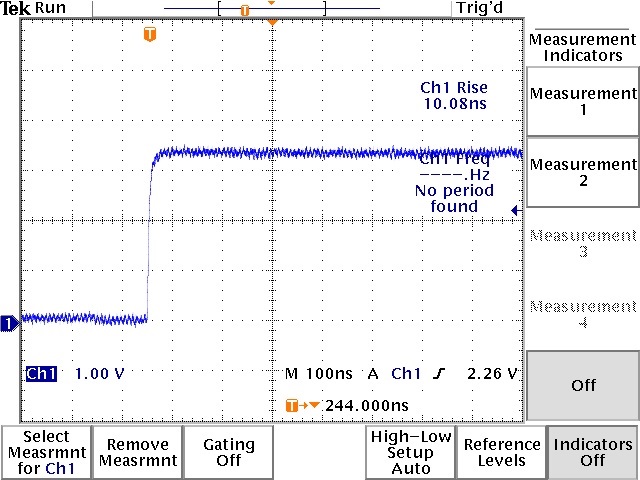

Because rise time in above figures was about 1.8ns, we have added 100ohm/100pF low pass RC filter to the SSI0CK, SSI0FS, SSI0RX.

The SPI communication problems disappear – no signal clipping was observed in temperature above 85 C degrees.

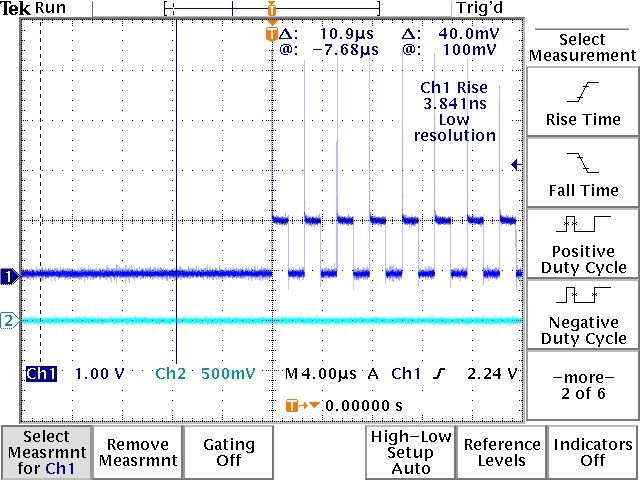

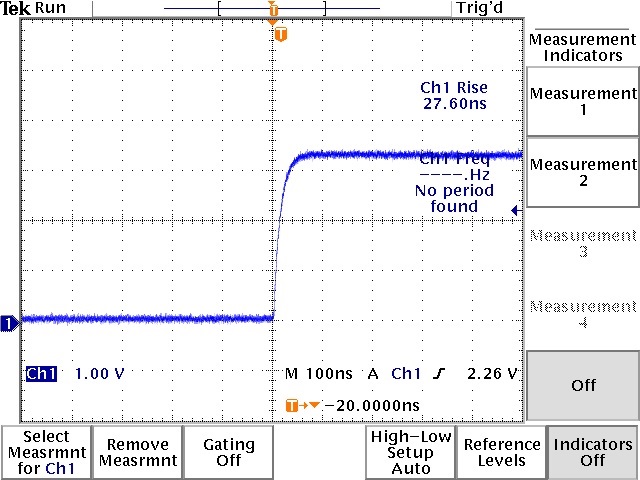

The signals after filtering are presented below (SPI clock is used as an example). The rise time is changed from 1.8ns to 28ns.

=========== SPI Clock signal: ===========

===========SSI0TX (this is not filtered output pin, the plot added for comparison purposes): ===========

Please confirm, that anyone has similar problems and the proposed solution works.

Best Regards

Igor