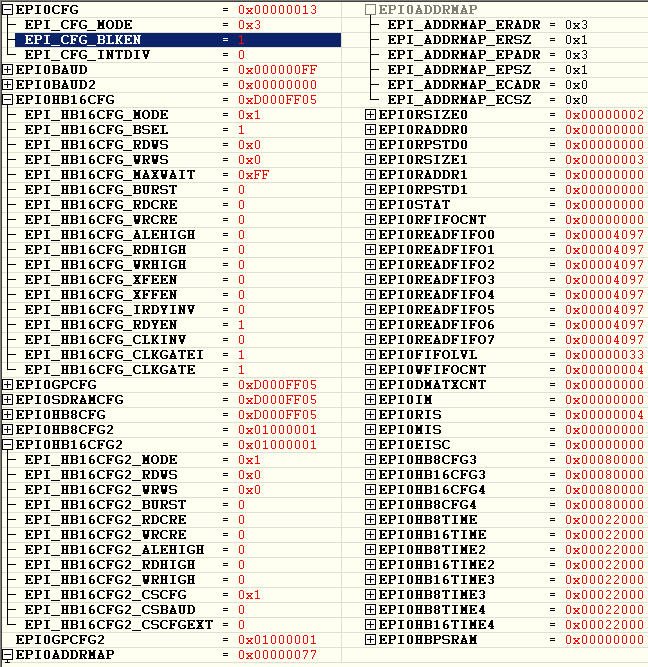

I'm setting up the EPI interface on a TM4C1294NCPDT on an EK-TM4C1294XL launchPad board. In HostBus16 mode I can write to the 16bit EPI bus but I cannot read from it. The addressing, byte selects, read pulse and chip select all function as expected. I see data appear on the bus when the read pulse goes active, but the data read from it always reads zero. Writes work fine except I don't see the bus being stalled for multiple writes when the iRDY signal goes low. I can read the status of the pin associated with iRDY with other code and it works okay but I need it working with the EPI transactions. I've tried the active state of iRDY set both ways round.

The EPI bus is being read with the assembler lines:

BASE_ADDRESS EQU 0x60000000

LDR R0, =BASE_ADDRESS

LDRH R1 [R0] ; load 16bits (Half word) from address 0x60000000

I've also tried reading all the addresses in the 64KB address range 0x60000000 through 0x6000FFFF with some of the bits on the data bus pulled high, but always get 0x0000. I feel I'm missing something here in terms of setup.

Some questions:

1) Anybody know what's going on? :) And why I can't read data in?

2) Do the FIFOs have to be enabled to read from the EPI bus? The datasheet is very good but not especially clear on this. The EPI block diagram suggests not.

3) Any idea why iRDY doesn't stall bus writes? Or does this only kick into life when the FIFOs are used?