Other Parts Discussed in Thread: ADS1255

Hi

I have been trying to continuously read out two ADCs (ADS1255) on SSI1 and SSI2 using the uDMA of the TM4C123 MCU.

The goal would be to have both ADCs running at 30kSPS, with DMA transfer sizes of 29 bursts of 4 bytes each in PingPong Mode.

I have my program currently set up to use the Timer DMA channels for sending 4-Byte bursts to the SSI TX FIFO at the ADC sampling rate. At the same time, the SSI RX DMA channels are configured for identically sized transfers copying data form the SSI RX FIFO to a buffer in memory.

My problem is now, that in order to reinitialize the DMA channels I had to use a seperate Timer interrupt, since I do not get any DMA done interrupts on the Timer or SSI interrupt vectors.

Going back to the TM4C123 Datasheet I found some conflicting information regarding this issue:

As stated in section 9.2.10:

"When a μDMA transfer is complete, the μDMA controller generates a completion interrupt on the interrupt vector of the peripheral. Therefore, if μDMA is used to transfer data for a peripheral and interrupts are used, then the interrupt handler for that peripheral must be designed to handle the μDMA transfer completion interrupt."

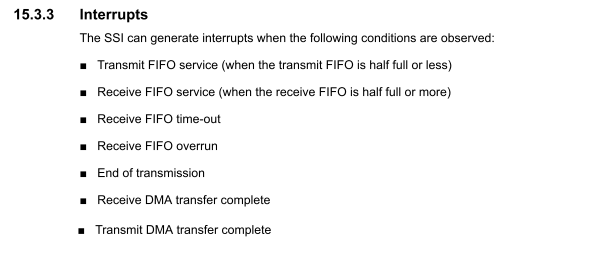

Accordingly, I find the following list of Interrupt events in the SSI Section of the datasheet: (I could not find any similar list in the General Purpose Timer section of the Datasheet)

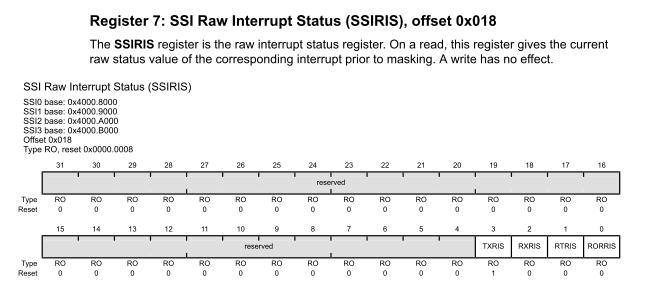

However, I look at the description of the SSIRIS register, there are no such interrupt bits defined at the locations that the TivaWare Functions would suggest (bits 4 and 5):

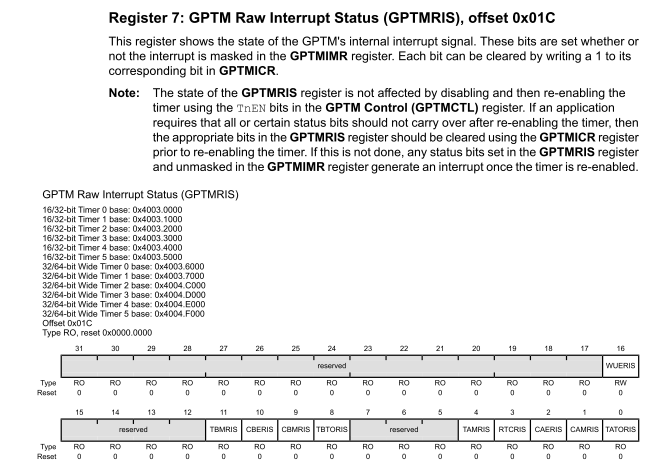

(As a side note, when looking into the TM4C129 datasheet, these bits seem to exist in the SSIRIS as well as the GPTMRIS registers).

How can I access the DMA completion interrupts in the TM4C123? Do they even exist?

Thanks in advance for any help or insights!