The Tiva TM4C129DNCZAD Microcontroller DATA SHEET includes the following paragraph in section 19.3.9 for UART Interrupts:

“The receive timeout interrupt is asserted when the receive FIFO is not empty, and no further data

is received over a 32-bit period when the HSE bit is clear or over a 64-bit period when the HSE bit

is set. The receive timeout interrupt is cleared either when the FIFO becomes empty through reading

all the data (or by reading the holding register), or when a 1 is written to the corresponding bit in the

UARTICR register.”

For the first sentence above, if there is simply no more data sent to the UART to receive, why should there be a Receive Timeout interrupt indicating an error?

That is, no further data is expected so why is that identified as a Receive Timeout?

Based on the second sentence, is the first sentence supposed to be interpreted something like as follows?

“If the Interrupt Service Routine (ISR) exits without reading all the data in the FIFO, a Receive Timeout interrupt will occur.”

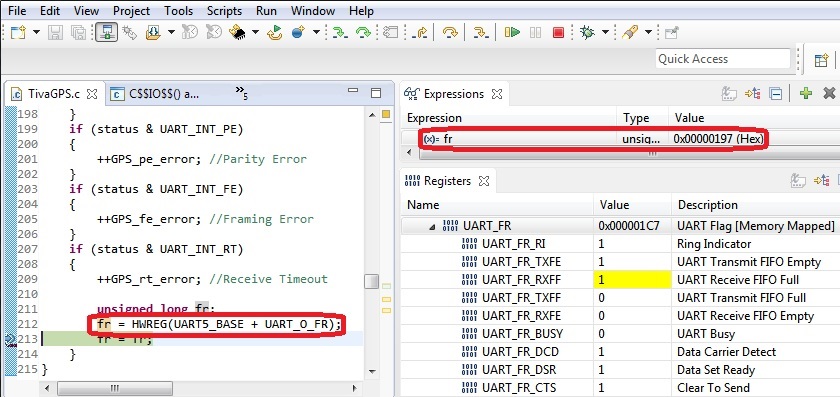

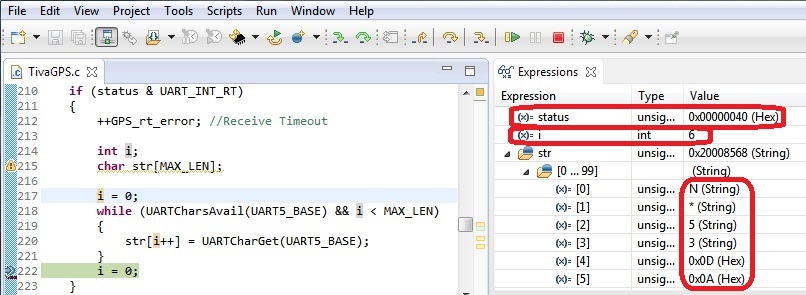

I have two UARTs running in a Tiva TM4C1290NCZAD (ARM Cortex M4F) for which the ISRs simply call the Tiva Peripheral Driver Library function UARTIntClear(), read all data available from the FIFO, and then return.

Therefore, since “The receive timeout interrupt is cleared when the FIFO becomes empty through reading all the data”, there should theoretically be no Receive Timeout interrupts.

However, there are Receive Timeout interrupts (for both UARTs).

I would like to know why Receive Timeout interrupts occur even when “the FIFO becomes empty through reading all the data” in the ISR.

Thank you for your time,

Tim