Other Parts Discussed in Thread: TM4C1294NCPDT, SN74AVC2T244, LSF0102

Hi

I am using SSI0 module of TM4C1294NCPDT micro controller in freescale legacy mode.

SPI mode used is SPO=0 (Clock polarity low) and SPH=1 (Capture on falling edge).

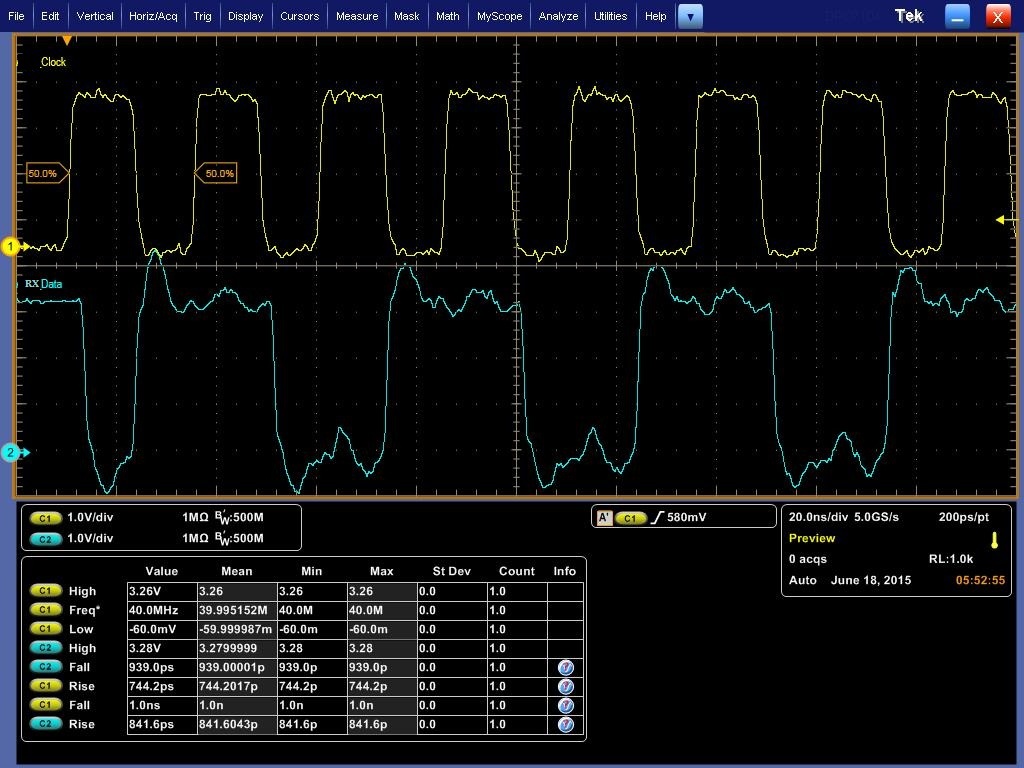

But due to very high propagation delay, RX data from slave looses synchronization with clock. The data is half clock period lagging behind clock.The data captured by MCU is completely different.(Below is the scopeshot captured for RX data with clock on MCU pins).

I have tried to use HSCLKEN bit in the SSI Control 1 (SSICR1) register which datasheet says can be used for faster timing and logic can be used to adjust clock to external data relationships.

But just by setting the HSCLKEN bit is not helping me to solve the problem.

I am not getting much detail in TI documentation on how to implement logic for adjusting clock to external data.

Does anybody have used this feature?

Can anybody help me to solve this problem?