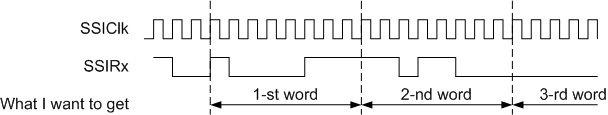

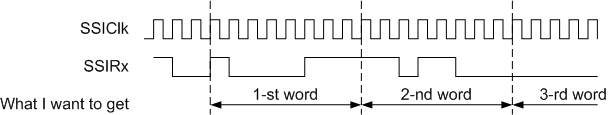

I strongly need to use SPI with DMA in the receiving mode without the frame synchronization. I tried to use Motorola modes (when SPI becomes active if you set 0 on the FSS pin) but I've got a fail. Regardless of which level which I set on the FSS pin SPI doesn't want to receive an information. It seems like receipt is possible only by the edge of the FSS signal not on the constant level on it. Is it true? Is it possible to receive without FSS at all?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.