Hi,

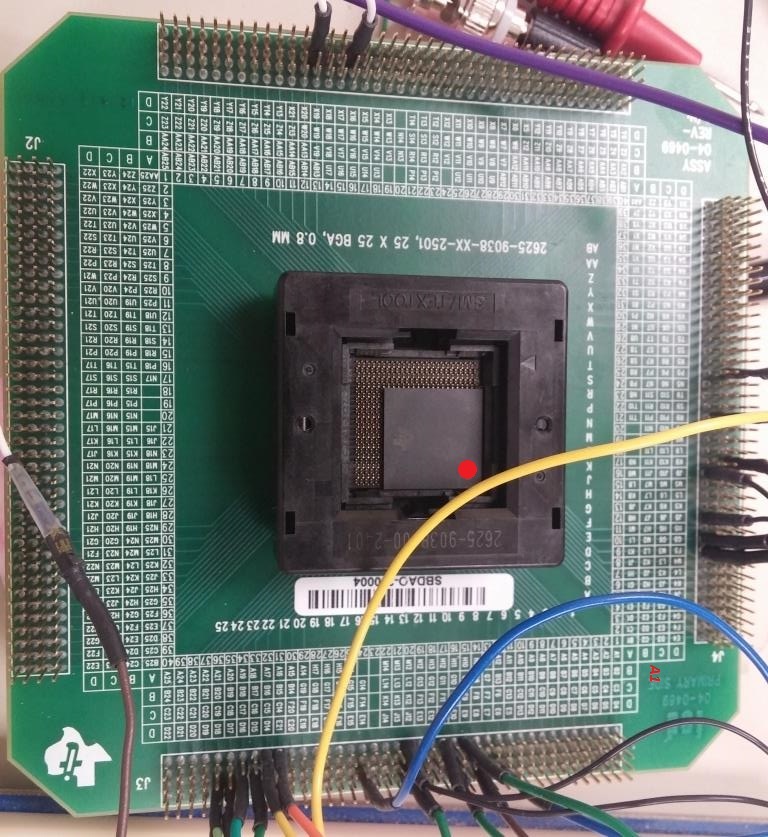

I am trying to bias the MCU on a BGA breakout board but the JTAG pins are stuck at zero. I'd like to confirm the connection is correct and adequate since not all PS pins/balls are connected

1.2V --> VCC (H10, F10, K12), VCCPLL(P11), consume 67mA with 16MHz external crystal and 52mA without crystal when just powered on

3.3V --> VCCIO (F14, P6, F6), VCCP (F8), VCCAD (W15), nPORRST (W7), nRST (B17). When nRST is floating, current is 3mA, when nRST is connected to 3.3V directly, the current through 3.3V supply is 44mA.

GND --> VSSAD (W16, W19), VSS (K10, M8, H8, M12, H12)

All the JTAG pins are connected to XDS100V2 emulator. All other pins are floating. TEST pin is grounded.

Here is the picture of the board.

I got the following JTAG error message during connection test

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\a0273331\AppData\Local\TEXASI~1\

CCS\ti\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Sep 4 2015'.

The library build time was '21:59:23'.

The library package version is '6.0.14.5'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

-----[The log-file for the JTAG TCLK output generated from the PLL]----------

There is no hardware for programming the JTAG TCLK frequency.

-----[Measure the source and frequency of the final JTAG TCLKR input]--------

There is no hardware for measuring the JTAG TCLK frequency.

-----[Perform the standard path-length test on the JTAG IR and DR]-----------

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-zero.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-zero.

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Test 1 Word 0: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 1: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 2: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 3: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 4: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 5: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 6: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 7: scanned out 0xFFFFFFFF and scanned in 0x00000000.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 1, skipped: 0, failed: 1

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted - 83.3 percent.

The JTAG IR Integrity scan-test has failed.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Test 1 Word 0: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 1: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 2: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 3: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 4: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 5: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 6: scanned out 0xFFFFFFFF and scanned in 0x00000000.

Test 1 Word 7: scanned out 0xFFFFFFFF and scanned in 0x00000000.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 1, skipped: 0, failed: 1

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted - 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

Is there anything wrong with the connection? Does the current meet the expectation?

Thanks,