Hello,

I have a product based on the TM4C123GE6PMI and I'm having crosstalk between ADC channels. My setup/configuration:

ADC0 Initial configuration:

//

// Initially configure ADC0

//

SysCtlADCSpeedSet(SYSCTL_ADCSPEED_500KSPS);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

SysCtlPeripheralEnable(SYSCTL_PERIPH_ADC0); // Enable ADC0 peripheral

// Set GPIO PE3 as an ADC input

GPIOPinTypeADC(GPIO_PORTE_BASE, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_3);

GPIOPinTypeADC(GPIO_PORTD_BASE, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_3);

ADC0 Mode configuration:

ADCSequenceConfigure(ADC0_BASE, 0, ADC_TRIGGER_ALWAYS, 0); // Configure over sampling ADCHardwareOversampleConfigure(ADC0_BASE, OverSample); // Configure Sequencer 0 to sample 4 channels each store in a step // Interrupt on step3 -> final step ADCSequenceDisable(ADC0_BASE, 0); ADCSequenceStepConfigure(ADC0_BASE, 0, 0, ADC_CTL_CH0); ADCSequenceStepConfigure(ADC0_BASE, 0, 1, ADC_CTL_CH1); ADCSequenceStepConfigure(ADC0_BASE, 0, 2, ADC_CTL_CH2); ADCSequenceStepConfigure(ADC0_BASE, 0, 3, ADC_CTL_CH3 | ADC_CTL_IE | ADC_CTL_END); // Register interrupt handler ADCIntRegister(ADC0_BASE, 0, ADC0IntHandler4ch_TestMode); // Clear interrupt flag ADCIntClear(ADC0_BASE, 0); // Enable interrupts ADCIntEnable(ADC0_BASE, 0);

So the Tiva part gets triggered and kicks off the ADC with this configuration pre-loaded. At power up the Initial configuration is run. After that and some other system configuring (GPIO, USB etc..) the mode configuration is run. This is run separately because the speed and number of channels are configured based on parameters stored in EEPROM. So the params might say run 1 channel at 500k or 4 channels at 1k etc...

The ADC0 is always configured to run at 500ksps per the

SysCtlADCSpeedSet(SYSCTL_ADCSPEED_500KSPS);

instruction. So if I want to run 4 channels I effectively get 125ksps/channel. The problem I'm seeing with is when I run 4 channels.

So, to recap the above configuration is what I'm using in this exact situation recording 4 channels with ADC0 speed set to 500k.

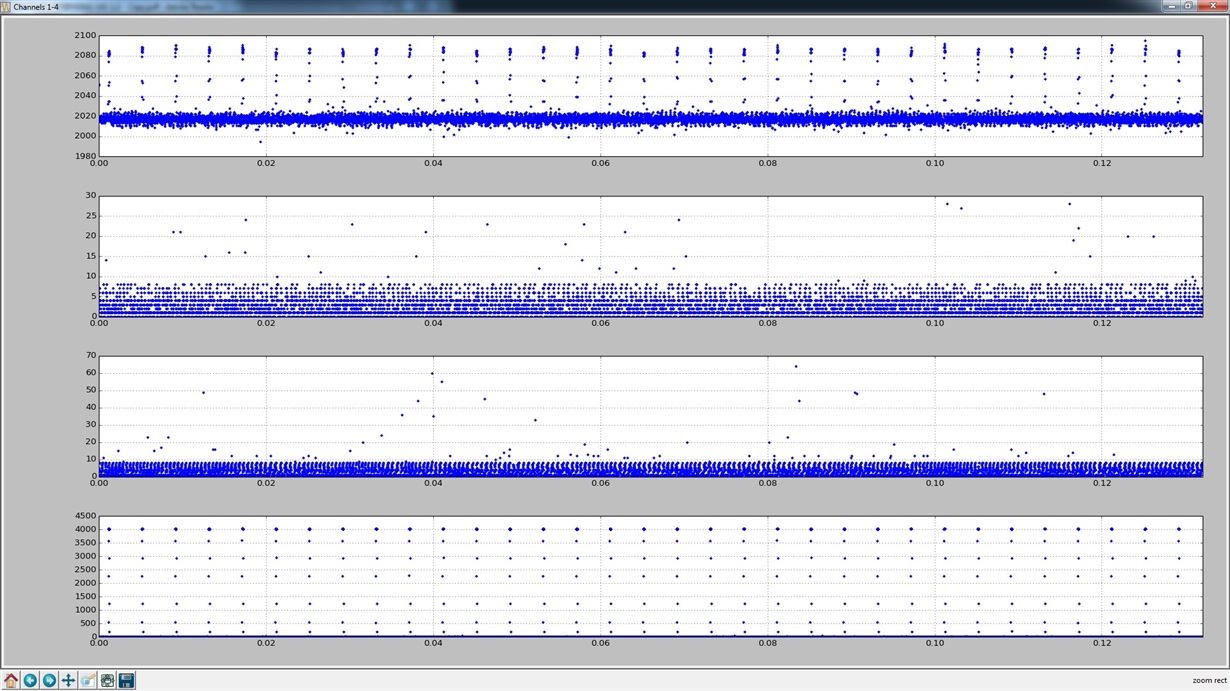

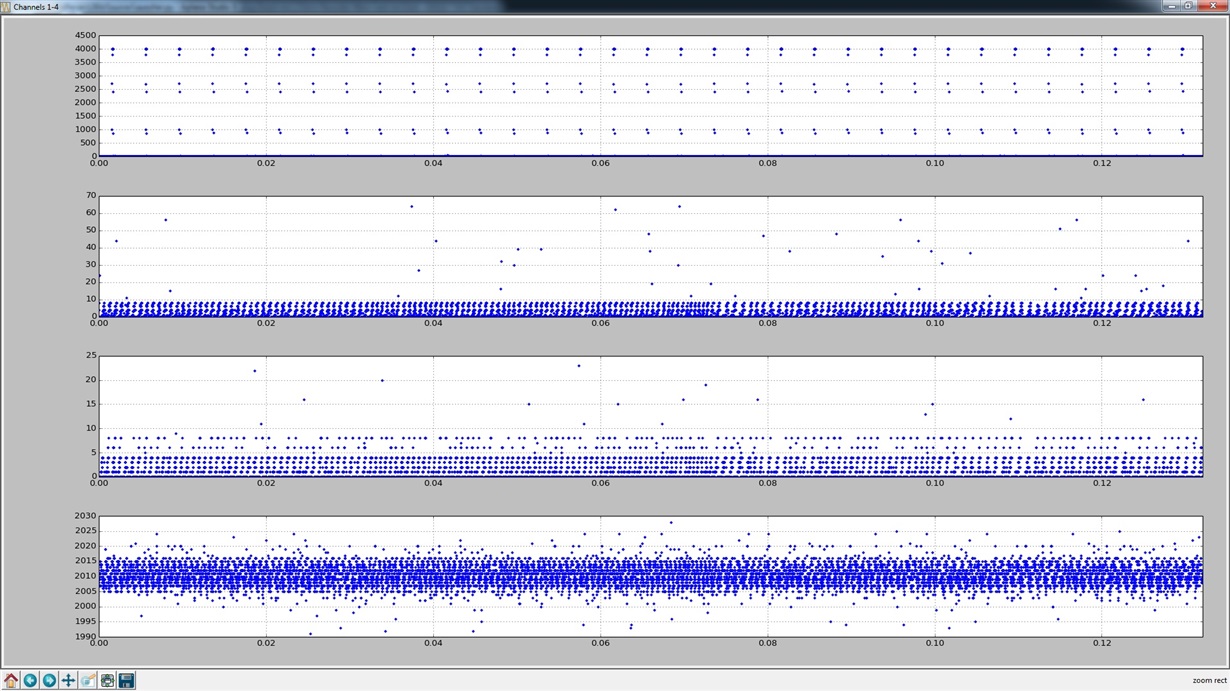

The problem I'm having is this: If I put a PWM signal into channel 4 and run with the ADC0 configured as above, I get a little bit of the signal in channel 4 bleeding over to channel 1. So in other words If I run a 3.3V pwm signal into channel 4 with channels 2 and 3 grounded I see the below plot...

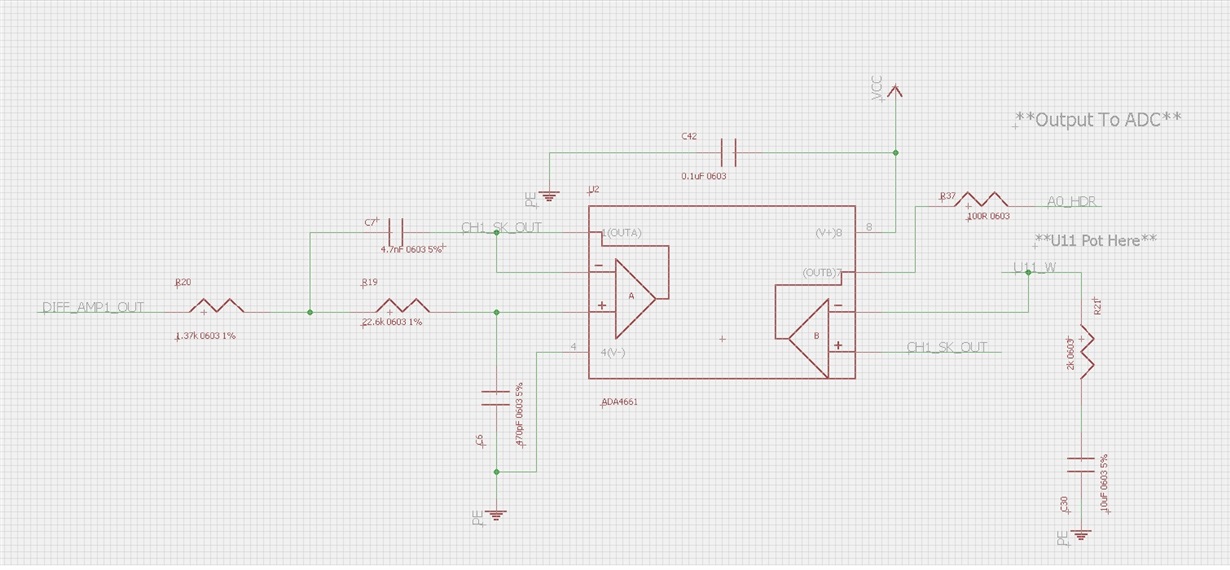

Channel 1 really should be around 0v (roughly) like channels 2 and 3. Some how channel 4's signal is getting into channel 1. I thought I would be pretty safe running this at 500k since it isn't the max speed. I would have though the adc cap could discharge pretty easily by then. I'm not sure exactly what is going on. The input of channel 1 has an op amp driving it, but the op amp is AC coupled. Shown below:

The PWM signal comes in through R20 (Sallen key LPF) and then into a gain stage. Between A0_HDR and U11_W nets is a digital POT which allows me to adjust the gain via I2C. The 100R is inline with the output as recommended by analog devices for stability. So yes, the 100R is IN SERIES with the ADC0 Channel1 that is experiencing this problem.

I don't see this problem when I put a scope probe at the input of channel1 and let the pwm signal run continuously through this analog circuit. I ONLY see this pulses on ch1 when I sample the four pins with the ADC. I'm not sure if this is a ADC configuration problem or a problem with the way I'm driving the channels, but I'm out of ideas troubleshooting and am looking for some new fresh perspectives/ideas.

If anyone has any insight it would be helpful.

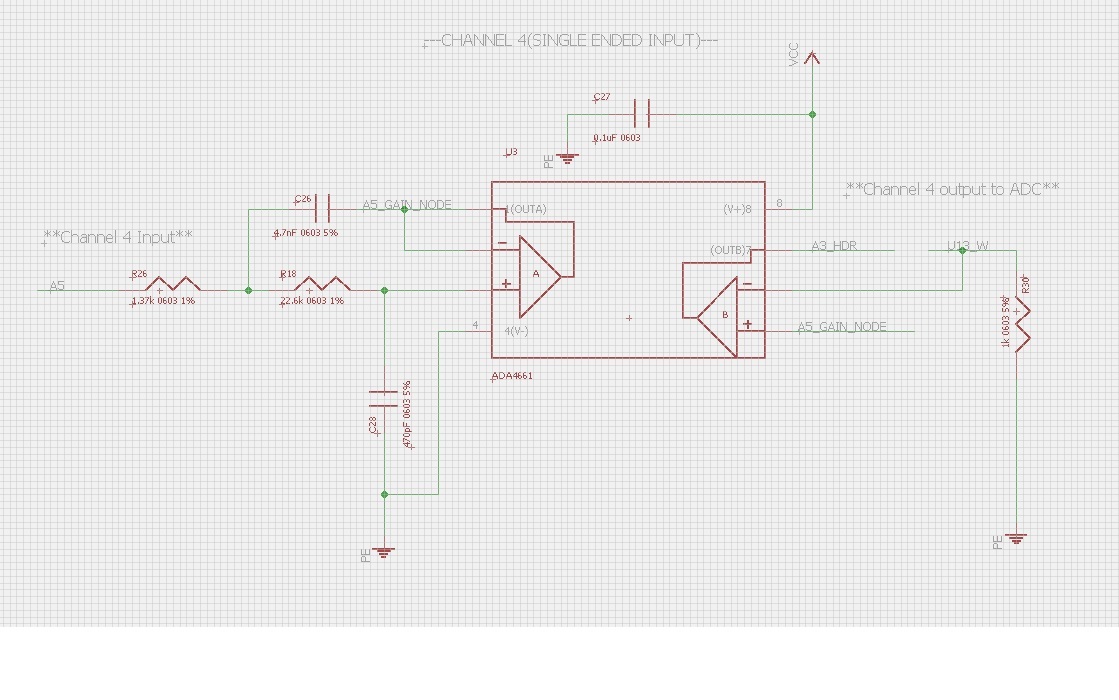

As a note for what circuits are driving what channels (ch1 -> ch4) the above op amp circuit is driving channels 1 and 2. The below circuit is driving channels 3 and 4. I DO NOT see this problem on channel 3 when the ADC channel 3 pin is ungrounded and left being driven by the below circuit so I'm leaning towards this possibly being an issue because ch1 and ch2 opamp circuits are ac coupled and don't drive a "DC" signal into the pins as the below circuit for ch3 and ch4 do.

The break between nets A3_HDR and U13_W is where the digital POT goes allowing me to adjust gain here just like above. The big difference is the AC coupled part but I don't understand how this could produce this problem.

Thanks,

Rob